Der physische Entwurf moderner Prozessoren dauert in der Regel Jahre und kostet je nach Komplexität und Prozesstechnologie Dutzende oder Hunderte Millionen Dollar. Halbleiter-Startup Null ASIC hat eine Plattform angekündigt, die den schnellen Zusammenbau eines hochgradig maßgeschneiderten Multi-Chiplet-System-in-Package (SiP) aus bekanntermaßen guten Chiplets ermöglicht. Die ChipMaker-Plattform soll die kundenspezifische Siliziumentwicklung demokratisieren.

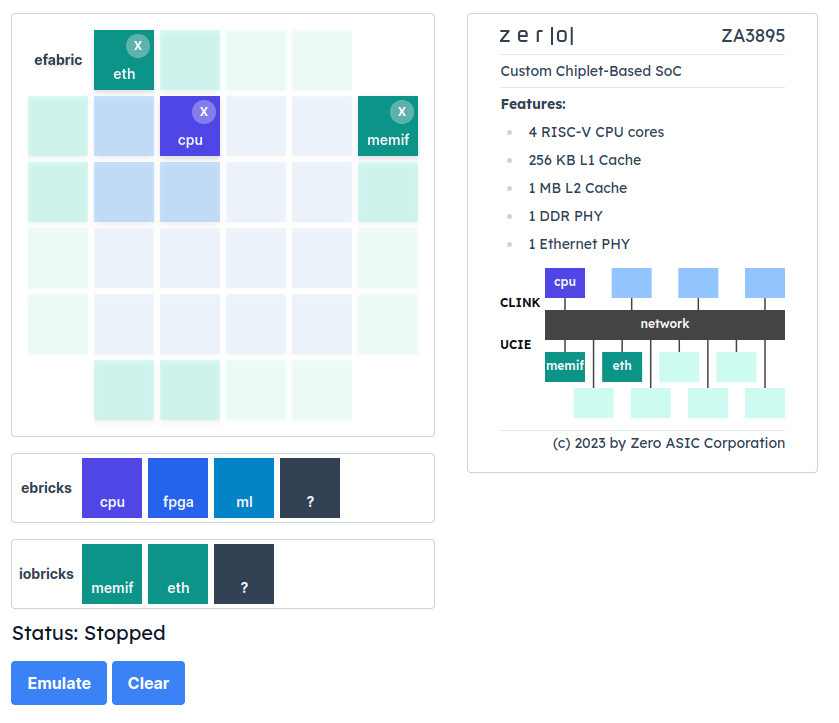

Die Entwicklung eines kundenspezifischen anwendungsspezifischen integrierten Schaltkreises (ASIC) vom Konzept bis zur Produktion ist für viele Startups zu langwierig und zu teuer. Die ChipMaker-Plattform von Zero ASIC vereinfacht den Prozess durch die Verwendung von Chiplet-basierten Designs, verbirgt die Komplexität des Schaltungsdesigns und ermöglicht es Benutzern, ihre benutzerdefinierten Designs schnell und genau zu testen und zu ändern, bevor sie die physischen Geräte bestellen. Dies alles wird mithilfe von Cloud-FPGAs (Field Programmable Gate Arrays) zur Implementierung des RTL-Quellcodes erreicht.

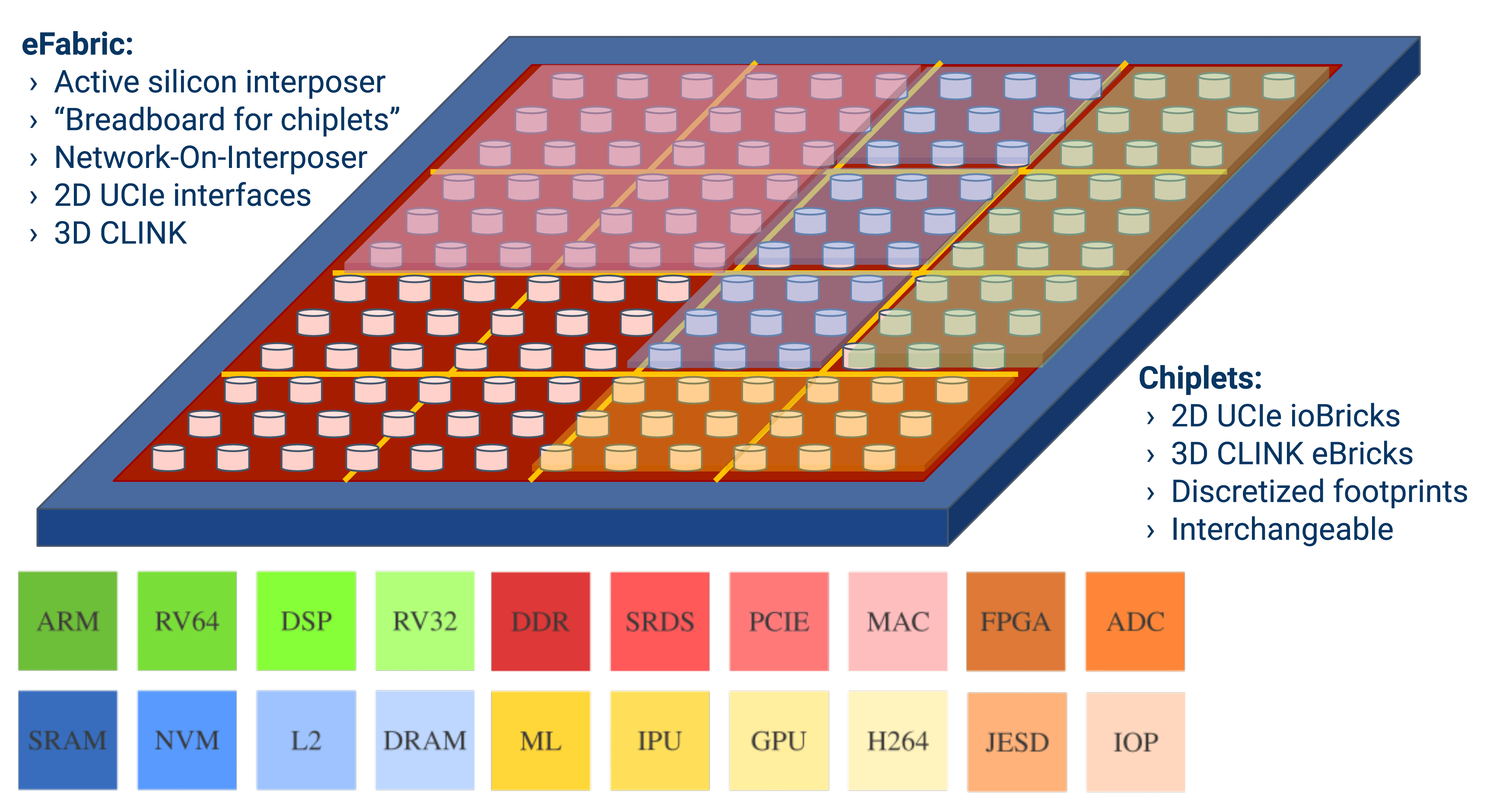

Die Plattform von Zero ASIC basiert auf eFabric, einem 3D-Interposer, der die Kommunikation von Chip zu Chip ermöglicht, und eBrick, einer Sammlung vorgefertigter 3D-Chiplets mit Plug-and-Play-Funktionen.

Der eFabric fungiert als dynamischer 3D-Interposer mit einer gitterartigen Struktur mit einer Halbierungsbandbreite auf dem Stoff von 512 Gbit/s/mm. Der 3D-Interposer erleichtert die Integration von Verarbeitungseinheiten mithilfe von 3D-verbundenen interoperablen eBrick-Chiplets mit einer Chiplet-3D-Bandbreite von 128 Gbit/s/mm2. Es unterstützt auch die Integration von Off-Package-IO-Funktionen durch 2D-verbundene UCIe-basierte ioBrick-Chiplets mit 128 Gbit/s/mm Chiplet-2D-Bandbreite.

Derzeit verfügt Zero ASIC über einen moderaten Katalog von 2 mm^2 eBrick-Chiplets, einschließlich einer Quad-Core-RISC-V-Linux-fähigen Dual-Issue-CPU, eingebettetem 5K-LUT-FPGA, 3 MB SRAM und 3 TOPS ML (Tera-Ops pro zweiter Beschleuniger für maschinelles Lernen. Diese Chiplets werden verwendet, um die Fähigkeiten der Plattform auf dem Open Compute Platform Summit/Open Chiplet Economy Center vom 17. bis 19. Oktober in San Jose, Kalifornien, zu demonstrieren.

Zero ASIC geht davon aus, dass der Katalog der eBrick-Chiplets im Laufe der Zeit erheblich erweitert wird. Dies wiederum wird es der ChipMaker-Plattform ermöglichen, immer rentabler zu werden, obwohl nicht bekannt gegeben wird, wie das Unternehmen dies erreichen will.

„Kundenspezifische anwendungsspezifische integrierte Schaltkreise (ASICs) bieten einen 10- bis 100-fachen Kosten- und Energievorteil gegenüber kommerziellen Standardgeräten (COTS), aber die enormen Entwicklungskosten machen ASICs für die meisten Anwendungen unbrauchbar“, sagte Andreas Olofsson, CEO und Gründer von Null ASIC. „Um die nächste Welle weltverändernder Siliziumgeräte zu bauen, müssen wir die Hürde für ASICs um Größenordnungen reduzieren. Unsere Mission bei Zero ASIC ist es, die Bestellung eines ASIC so einfach zu machen wie die Bestellung von Katalogteilen bei einem Elektronikhändler.“

Es klingt auf jeden Fall interessant. Ob es tatsächlich funktioniert und an Fahrt gewinnt, bleibt abzuwarten.