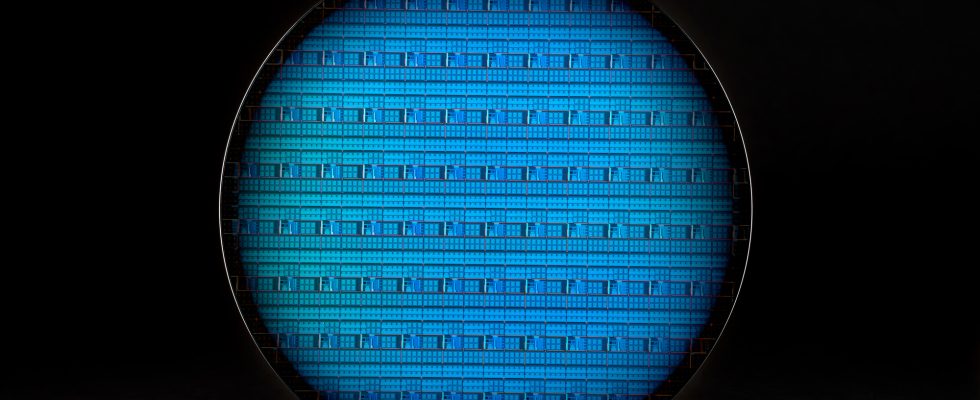

Quantenhardware-Forscher von Intel haben einen kryogenen 300-Millimeter-Probeprozess entwickelt, um mithilfe komplementärer Metalloxidhalbleiter-Herstellungstechniken (CMOS) umfangreiche Daten über die Leistung von Spin-Qubit-Geräten über ganze Wafer hinweg zu sammeln.

Die Verbesserungen der Qubit-Geräteausbeute in Kombination mit dem Hochdurchsatz-Testverfahren ermöglichten es den Forschern, deutlich mehr Daten zur Analyse der Einheitlichkeit zu erhalten, ein wichtiger Schritt, der zur Skalierung von Quantencomputern erforderlich ist. Die Forscher fanden außerdem heraus, dass Einzelelektronenbauelemente aus diesen Wafern eine gute Leistung erbringen, wenn sie als Spin-Qubits betrieben werden und eine Gate-Genauigkeit von 99,9 % erreichen. Diese Genauigkeit ist die höchste, die für Qubits berichtet wird, die ausschließlich in der CMOS-Industrie hergestellt werden.

Die geringe Größe von Spin-Qubits mit einem Durchmesser von etwa 100 Nanometern macht sie dichter als andere Qubit-Typen (z. B. supraleitend), sodass komplexere Quantencomputer auf einem einzigen Chip derselben Größe hergestellt werden können. Der Herstellungsansatz wurde mithilfe der Extrem-Ultraviolett-Lithographie (EUV) durchgeführt, wodurch Intel diese geringen Abmessungen erreichen und gleichzeitig in großen Stückzahlen produzieren konnte.

Die Realisierung fehlertoleranter Quantencomputer mit Millionen einheitlicher Qubits erfordert äußerst zuverlässige Herstellungsprozesse. Aufbauend auf seinem langjährigen Know-how in der Transistorherstellung ist Intel führend bei der Herstellung von Silizium-Spin-Qubits, die Transistoren ähneln, und nutzt dabei seine hochmodernen 300-Millimeter-CMOS-Fertigungstechniken, mit denen routinemäßig Milliarden von Transistoren pro Chip hergestellt werden.

Aufbauend auf diesen Erkenntnissen plant Intel, weitere Fortschritte bei der Verwendung dieser Techniken zu machen, um mehr Verbindungsschichten hinzuzufügen, um 2D-Arrays mit erhöhter Qubit-Anzahl und Konnektivität herzustellen, und außerdem die Demonstration von Zwei-Qubit-Gattern mit hoher Wiedergabetreue in seinem industriellen Fertigungsprozess. Die Hauptpriorität wird jedoch weiterhin darin bestehen, Quantengeräte zu skalieren und die Leistung mit dem Quantenchip der nächsten Generation zu verbessern.