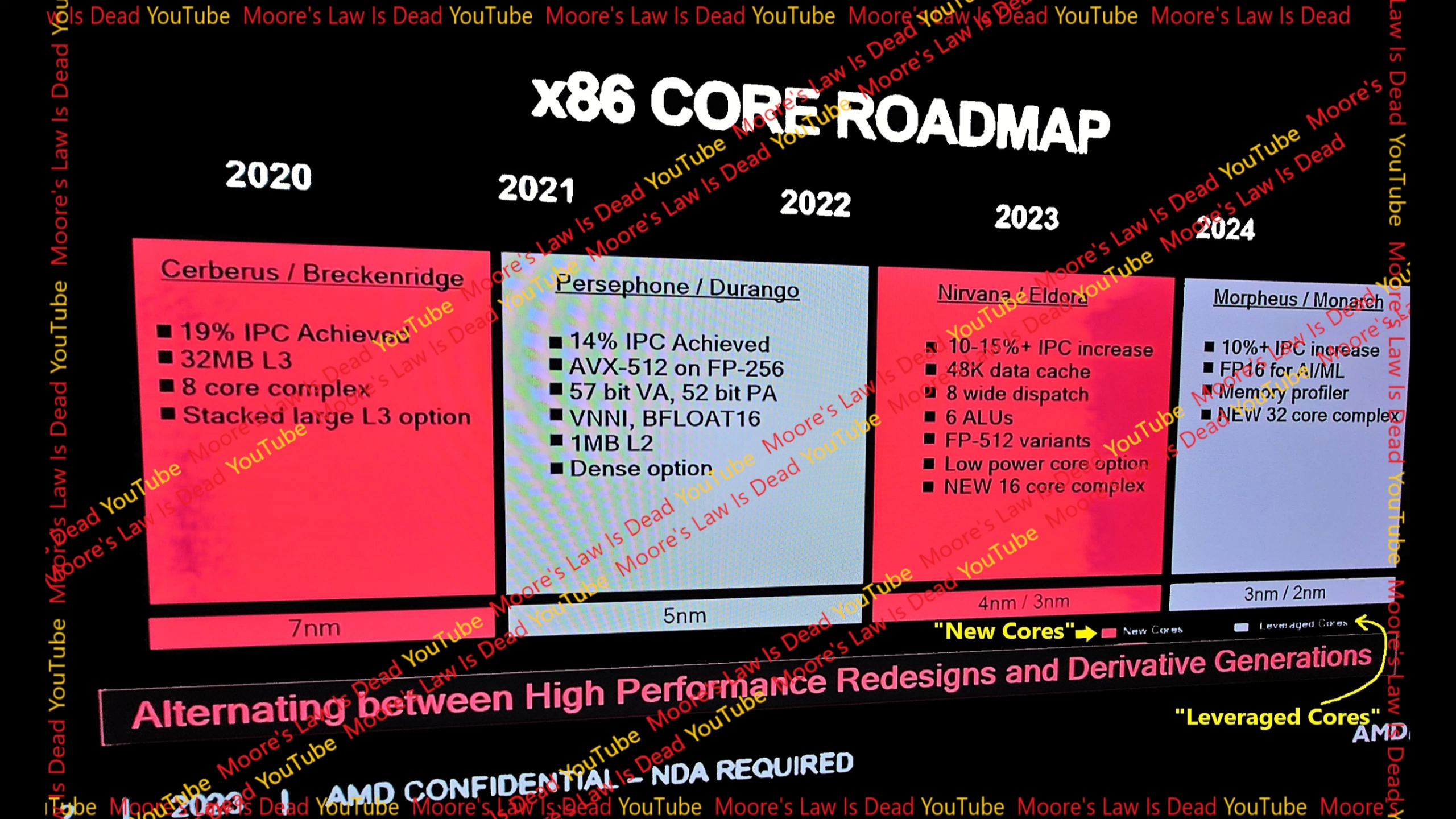

Youtube Kanal Moores Gesetz ist tot haben zwei neue, angeblich offizielle AMD-Folien durchgesickert, in denen die wichtigsten Spezifikationen und IPC-Ziele für Zen 5 und Zen 6 detailliert beschrieben werden. Die neuen Folien berichten, dass Zen 5 eine bedeutende architektonische Überarbeitung gegenüber Zen 4 sein wird und 10 bis 15 % IPC-Verbesserungen oder mehr anstrebt. Berichten zufolge wird Zen 5 zum ersten Mal auch 16-Kern-CCXs enthalten. Bevor wir weitermachen, müssen wir diesem Bericht eine ordentliche Portion Salz hinzufügen.

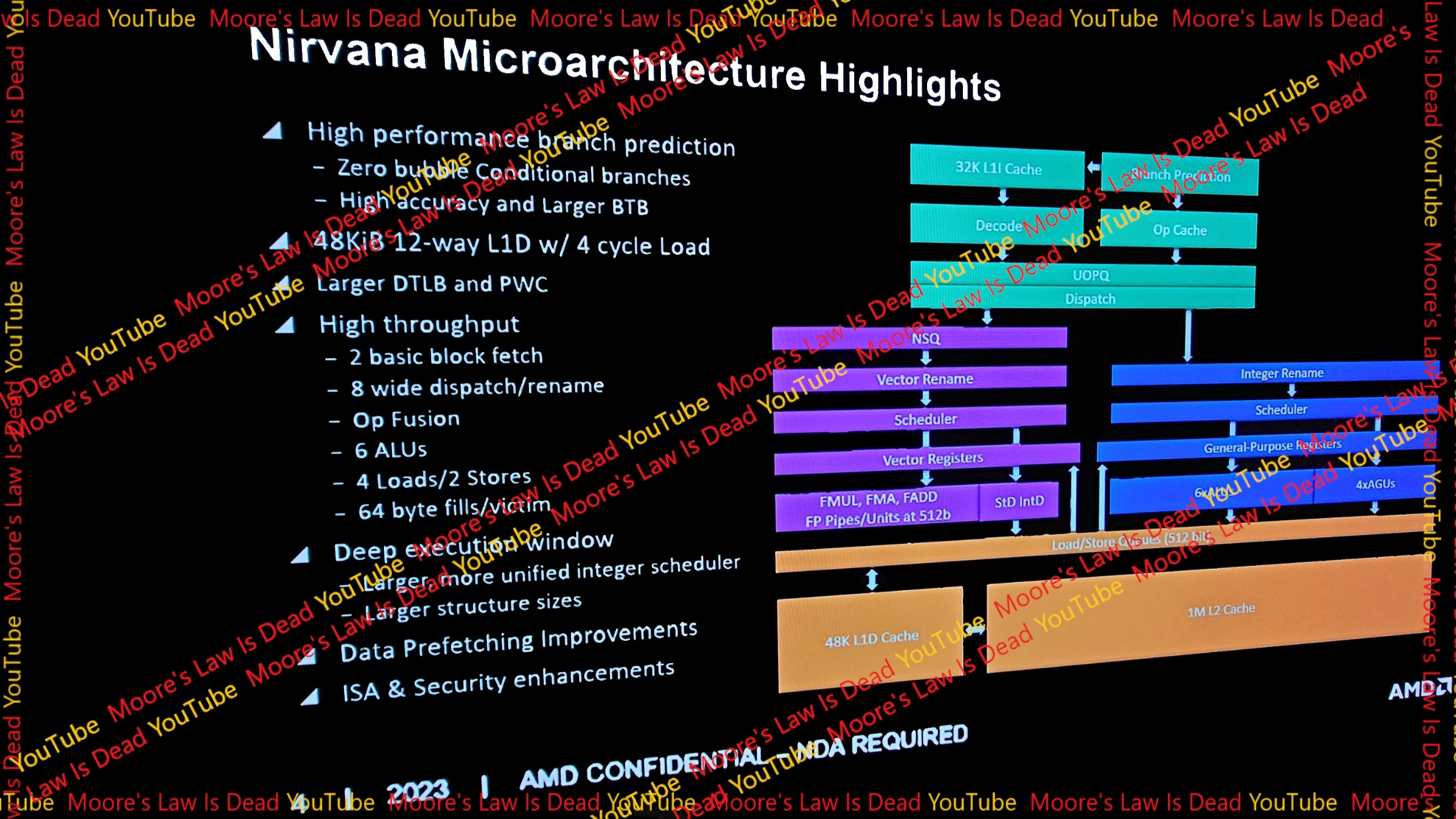

Die Liste der Verbesserungen am Zen 5-Kern ist recht umfangreich. Die größten Zuwächse betreffen den L1-Cache, den Branch Predictor, das Ausführungsfenster und den Kernverarbeitungsdurchsatz. Der Verzweigungsprädiktor hat bedingte Verzweigungen ohne Blasen, eine hohe Genauigkeit und einen größeren BTB erhalten. Die L1-Cache-Größe des Zen 5 ist von 32 KB beim Zen 4 auf jetzt 48 KB beim Zen 5 gewachsen.

Der Durchsatz des Chips wurde Berichten zufolge erheblich verbessert und umfasst 2 grundlegende Blockabrufeinheiten, 8 Wide-Dispatch/Rename-Einheiten, 6 ALUs, 4 Lade- und 2 Speichereinheiten und mehr. Berichten zufolge hat der Scheduler jetzt eine größere Strukturgröße und der Integer-Scheduler ist größer und einheitlicher als frühere Designs. Die Folie listet neben ISA- und Sicherheitsverbesserungen auch zusätzliche Verbesserungen beim Daten-Prefetch auf, geht jedoch nicht auf spezifische Details ein.

Eine weitere erhebliche Verbesserung, die aus den durchgesickerten Folien hervorgeht, ist die Kernkonfiguration der CCXs (Kernkomplexe) des Zen 5, die von 8 auf 16 verdoppelt wurde. Die neue Änderung ist das erste Mal seit Zen 2, dass AMD sich die Mühe gemacht hat, die Kernanzahl zu erhöhen seine CCXs, was bedeutet, dass wir in Zukunft einen 32-Kern „Ryzen 9 8950X“ sehen könnten.

Wir wissen noch nicht, welche Kerntypen diese neuen Zen 5-Kerncluster haben werden. Die Hälfte der Kernanzahl des Zen 5 könnte vollständig auf Zen 5c-Effizienzkerne entfallen, oder der gesamte Stapel könnte aus Vanille-Zen 5-Leistungskernen bestehen. Es könnte sich um eine Mischung aus beidem handeln, da die Folien von AMD darauf hindeuten, dass es verschiedene Modelle mit FP-512-Unterstützung und einige Modelle mit stromsparenden Kernen geben wird.

Es ist erwähnenswert, dass diese Folien ausschließlich auf die Enterprise-Server-Chips (EYPC) von AMD ausgerichtet sind und nicht auf die Mainstream-Desktop-CPUs für Endverbraucher. Erwarten Sie also nicht, dass im nächsten Jahr jedes Detail in die Ryzen 8000-Chips einfließt, wie zum Beispiel die FP-512-Unterstützung. Aber im Allgemeinen könnten die zugrunde liegenden Architekturspezifikationen Eingang in den Ryzen 8000 finden.

Die durchgesickerten Folien zeigen auch zusätzliche Prognosen zur Zen-6-Architektur von AMD. Die Folie zeigt, dass Zen 6 ein geschätztes IPC-Ziel von mindestens 10 %, FP16 für KI/maschinelles Lernen und einen neuen Speicherprofiler haben wird. Schließlich wird im letzten Aufzählungspunkt erwähnt, dass AMD die Anzahl der Kerne pro CCD noch einmal verdoppeln wird, nämlich von 16 auf 32 Kerne. Es besteht eine gute Chance, dass diese zweite Verdoppelung der Kernzahl langsamere/kompaktere Zen-6-Effizienzkerne umfassen wird, aber die Tatsache, dass AMD die Kernzahl in weniger als drei Generationen vervierfachen könnte, ist dennoch beeindruckend.

Zen 5 ist AMDs CPU-Architektur der nächsten Generation, die voraussichtlich 2024 mit AMDs Desktop- und Mobilchips der Ryzen 8000-Serie auf den Markt kommen wird. Und denken Sie daran, dass wir all diese Informationen mit Vorsicht genießen müssen, wenn man bedenkt, wie weit wir von einem offiziellen Start entfernt sind.