Laut DigiTimes, TSMC beschleunigt die Auftragsvergabe bei Backend-Ausrüstungslieferanten, da es einen Expansionsplan für seine Chip-on-Wafer-on-Substrat (CoWoS)-Verpackungskapazität startet. Der Mangel an Rechen-GPUs für künstliche Intelligenz und Hochleistungsrechnen, die Nvidia weitgehend dominiert, wird hauptsächlich auf die begrenzten Produktionskapazitäten von CoWoS-Paketen von TSMC zurückgeführt.

Berichten zufolge plant TSMC, seine derzeitige CoWoS-Kapazität von 8.000 Wafern pro Monat auf 11.000 Wafer pro Monat bis Ende 2023 und dann auf etwa 14.500 – 16.600 Wafer bis Ende 2024 zu erhöhen. Zuvor gab es Gerüchte, dass Nvidia seine CoWoS-Kapazität erhöhen würde bis Ende 2024 auf 20.000 Wafer pro Monat. Bedenken Sie, dass die Informationen aus inoffiziellen Quellen stammen und möglicherweise ungenau sind.

Große Technologiegiganten wie Nvidia, Amazon, Broadcom, Cisco und Xilinx haben alle ihre Nachfrage nach der fortschrittlichen CoWoS-Verpackung von TSMC gesteigert und verbrauchen jeden Wafer, den sie bekommen können. Laut DigiTimes war TSMC daher gezwungen, die Bestellungen für notwendige Ausrüstung und Materialien zu erneuern. Die Produktion von KI-Servern ist erheblich gestiegen, was die ohnehin schon starke Nachfrage nach diesen fortschrittlichen Paketierungsdiensten weiter anheizt.

Nvidia hat bereits 40 % der verfügbaren CoWoS-Kapazität von TSMC für das kommende Jahr gebucht. Aufgrund des gravierenden Mangels hat Nvidia jedoch damit begonnen, Optionen bei seinem Zweitlieferanten zu prüfen und Bestellungen bei Amkor Technology und United Microelectronics (UMC) aufzugeben, obwohl diese Bestellungen relativ klein sind, heißt es in dem Bericht.

Um den gestiegenen CoWoS-Verpackungsbedarf zu decken, arbeitet TSMC mit mehreren Lieferanten aus der ganzen Welt zusammen, darunter Rudolph Technologies mit Sitz in den USA, Disco aus Japan und SÜSS MicroTec aus Deutschland sowie die taiwanesischen Experten Grand Process Technology (GPTC) und Scientech. Die Zulieferer stehen unter Druck, bis Mitte 2024 knapp 30 Sätze relevanter Werkzeuge bereitzustellen.

TSMC hat auch mit der Umsetzung strategischer Änderungen begonnen, beispielsweise mit der Umverteilung eines Teils seiner InFO-Produktionskapazität von seinem nordtaiwanischen Standort in Longtan in seinen Southern Taiwan Science Park (STSP). Außerdem wird die Erweiterung des Longtan-Standorts beschleunigt vorangetrieben. Darüber hinaus steigert TSMC seine interne CoWoS-Produktion und lagert einen Teil seiner OS-Fertigung an andere Montage- und Testunternehmen (OSAT) aus. Beispielsweise war Siliconware Precision Industries (SPIL) einer der Nutznießer dieser Outsourcing-Initiative.

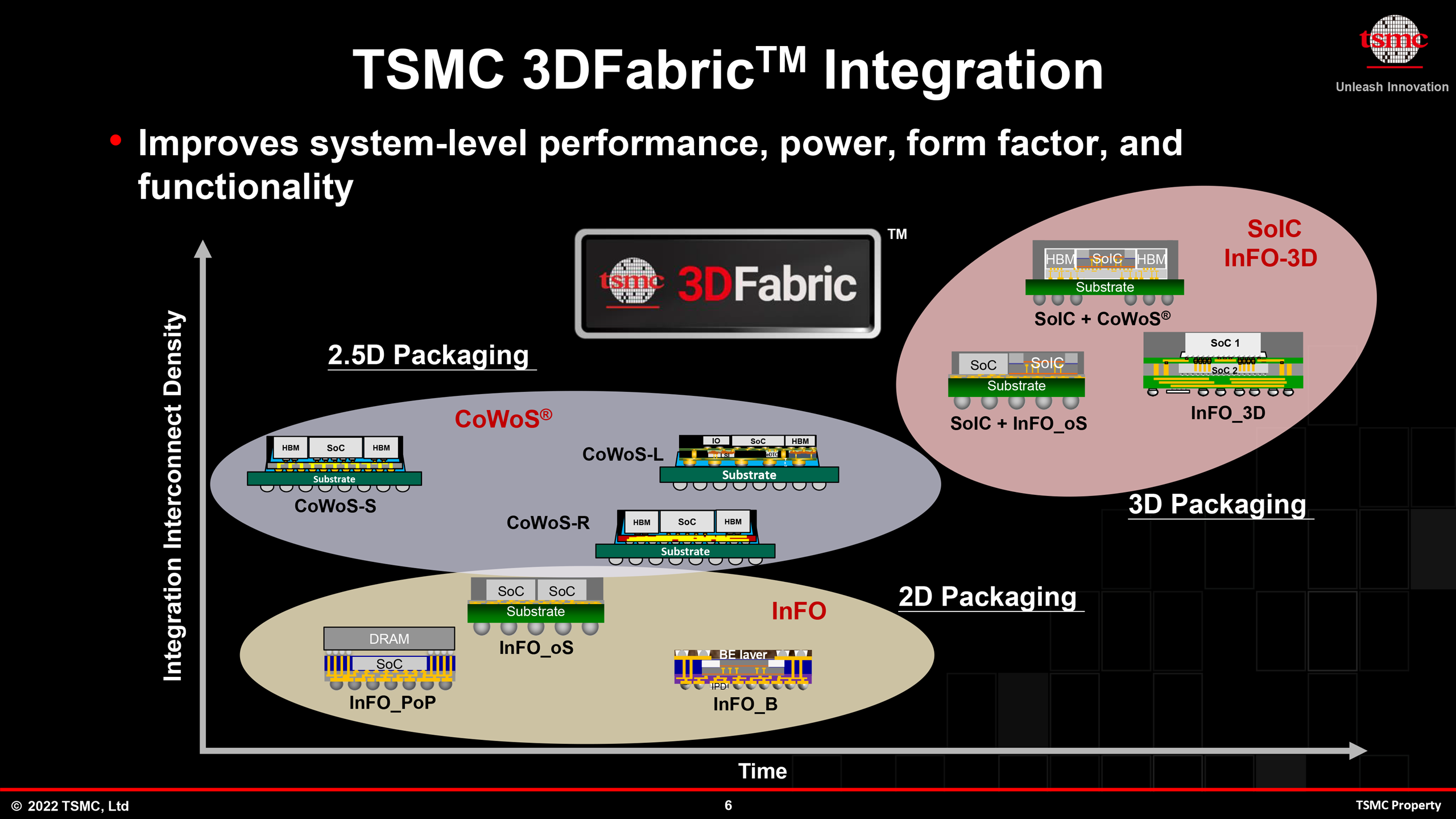

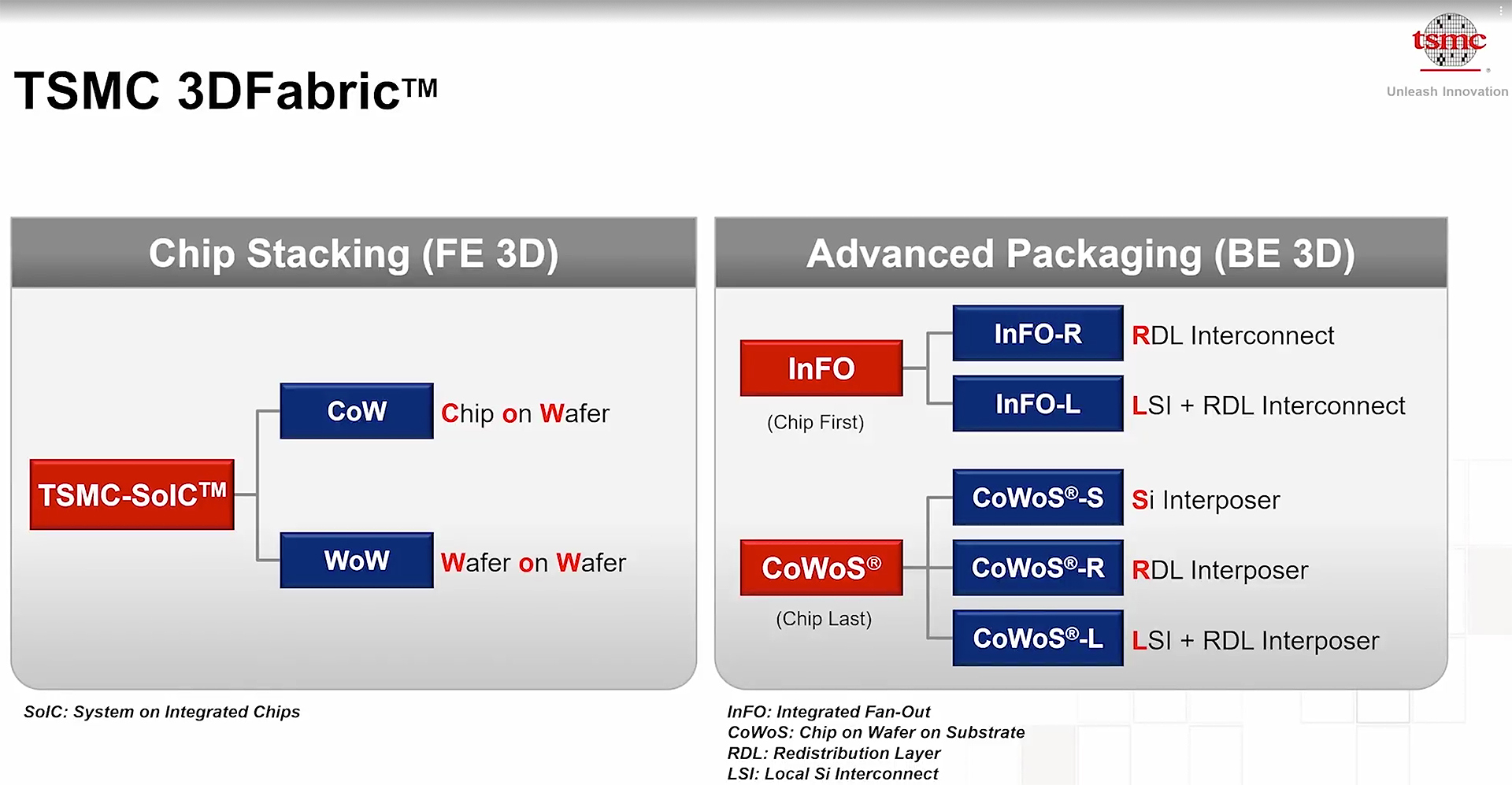

TSMC hat seine eröffnet Erweiterte Backend-Fab-6-Funktion letzte Woche. Das Unternehmen wird seine fortschrittliche Paketierungskapazität für seine Frontend-3D-Stacking-SoIC-Technologien (CoW, WoW) und Backend-3D-Paketierungsmethoden (InFO, CoWoS) erweitern. Derzeit ist die Fabrik für SoIC bereit. Das Advanced Backend Fab 6 kann rund eine Million 300-mm-Wafer pro Jahr verarbeiten und jährlich über 10 Millionen Teststunden durchführen, wobei der Reinraumraum größer ist als der Reinraumraum aller anderen TSMC-Hochleistungsverpackungsanlagen zusammen.

Zu den beeindruckendsten Merkmalen des Advanced Backend Fab 6 gehört das umfassende intelligente automatisierte Fünf-in-Eins-Materialtransportsystem. Das System steuert den Produktionsfluss, erkennt Fehler sofort und erhöht so den Ertrag. Dies ist bei komplexen Multi-Chiplet-Baugruppen wie dem MI300 von AMD von entscheidender Bedeutung, da Verpackungsfehler alle Chiplets sofort unbrauchbar machen, was zu erheblichen Verlusten führt. Mit Datenverarbeitungsfunktionen, die 500-mal schneller als der Durchschnitt sind, kann die Anlage umfassende Produktionsaufzeichnungen führen und jedes verarbeitete Werkzeug nachverfolgen.

Nvidia nutzt CoWoS für seine äußerst erfolgreichen Rechen-GPUs A100, A30, A800, H100 und H800. AMDs Instinct MI100, Instinct MI200/MI200/MI250X und der kommende Instinct MI300 nutzen ebenfalls CoWoS.