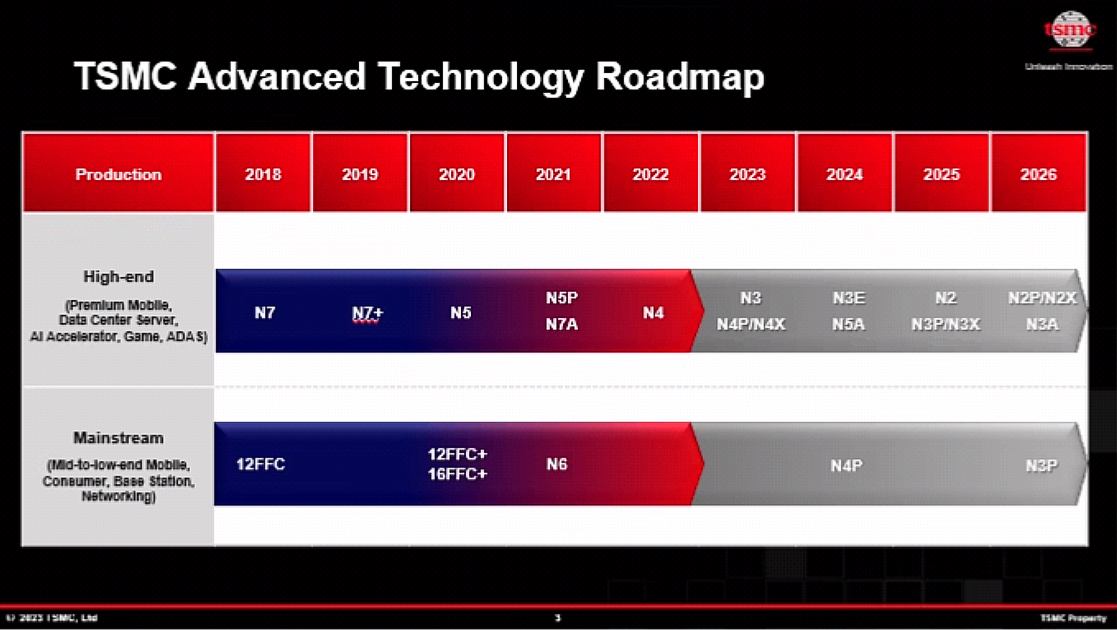

Auf dem North American Technology Symposium 2023 TSMC enthüllt Weitere Informationen zu seinen kommenden Prozesstechnologien der 2-nm-Klasse, die 2025 – 2026 produktionsbereit sein sollen Transistordichte erhöhen. Darüber hinaus plant TSMC N2X, einen Knoten, der darauf ausgelegt ist, maximale Leistung und Unterstützung für höhere Spannungen zu liefern.

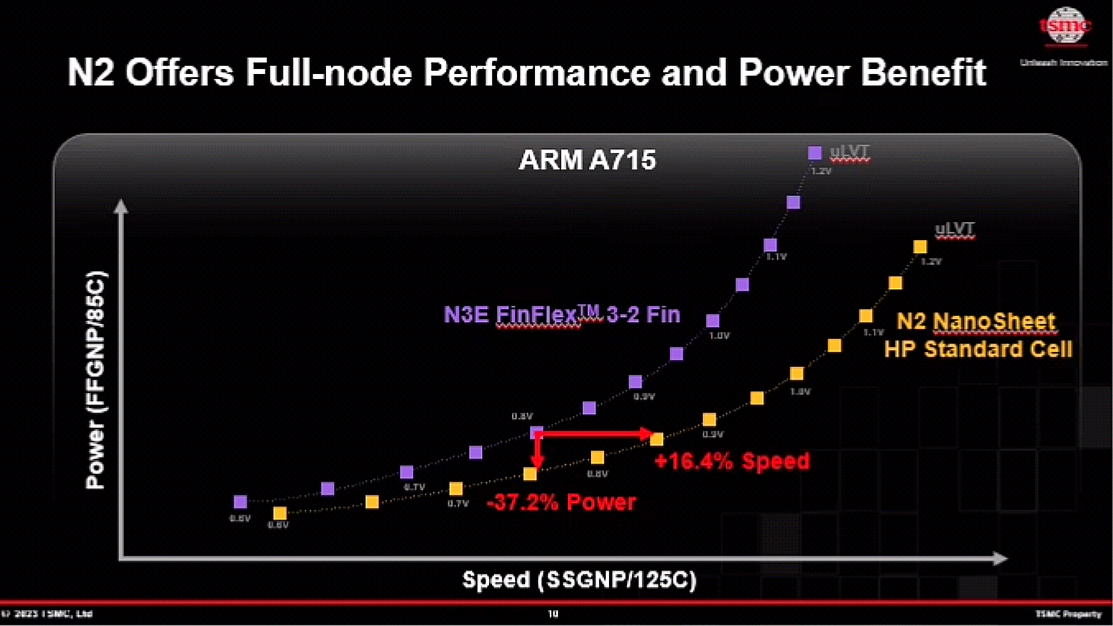

N2 bietet Full-Node-Vorteile

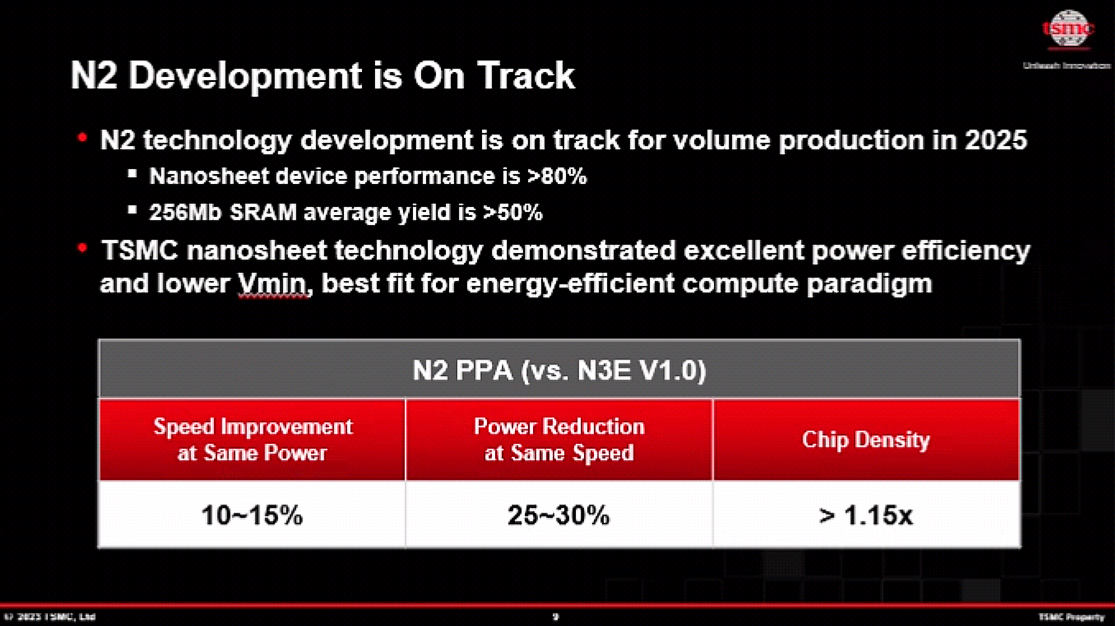

Die ursprüngliche N2-Prozesstechnologie von TSMC, die irgendwann im Jahr 2025 in die Massenproduktion gehen soll, führt Gate-All-Around (GAA) Nanosheet-Transistoren ein. Im Vergleich zu N3E verspricht der neue Knoten eine Leistungssteigerung um 10 % bis 15 % bei identischer Leistung und Transistoranzahl oder eine Verringerung des Stromverbrauchs um 25 % bis 30 % bei gleicher Frequenz und Komplexität. In Bezug auf die Skalierung verzichtet TSMC darauf, detaillierte Zahlen bereitzustellen, sagt jedoch, dass die neue Fertigungstechnologie eine Erhöhung der Chipdichte um 15 % ermöglichen wird, was ein mehrdeutiger Begriff ist, da er einen hypothetischen IC mit 50 % Logik und 30 % SRAM widerspiegelt und 20 % analoge Schaltungen.

Der N2-Fortschritt von TSMC scheint wie geplant zu verlaufen. Auf seinem Symposium gab TSMC bekannt, dass die Leistung seines Nanosheet-GAA-Transistors über 80 % seiner Zielspezifikationen erreicht hat und dass die durchschnittliche Ausbeute eines 256-MB-SRAM-Test-IC 50 % übersteigt.

N2P: Stromschiene auf der Rückseite für höhere Leistungseffizienz

Während N2 handfeste Vorteile gegenüber N3E bietet, verspricht sein Nachfolger N2P noch beeindruckender zu werden. Der 2-nm-Prozess der zweiten Generation von TSMC soll ein Backside-Power-Delivery-Network (PDN) beinhalten, das darauf ausgelegt ist, die Transistorleistung zu erhöhen, den Stromverbrauch zu senken, die Transistordichte zu erhöhen und das Risiko von Interferenzen zwischen Daten- und Stromkabeln im Chip zu eliminieren.

Backside Power Delivery ist eine der wichtigsten Innovationen der letzten Jahre, da Back-End-of-Line (BEOL) und Kontaktwiderstände seit einiger Zeit die größten Herausforderungen der Chiphersteller darstellen. Durch die Verlagerung von Stromschienen auf die Rückseite des Wafers trennt die Stromversorgung auf der Rückseite die E/A- und Stromverdrahtung und mindert Probleme mit erhöhten Via-Widerständen im BEOL.

Obwohl TSMC keine konkreten Zahlen zu den Vorteilen von N2P in Bezug auf Leistung, Leistung und Fläche (PPA) gegenüber N2 vorgelegt hat, sagen einige Analysten, dass Backside PDN zu einem einstelligen Rückgang des Stromverbrauchs und einer zweistelligen Zunahme der Transistordichte führen könnte. In Anbetracht dessen, dass TSMC wahrscheinlich weitere Optimierungen an N2P vornehmen wird, ist zu erwarten, dass diese Technologie sowohl in Bezug auf die Leistungseffizienz als auch in Bezug auf die Transistordichte deutlich fortschrittlicher sein wird als N2 und N3.

TSMC geht davon aus, dass N2P im Jahr 2026 für die Hochvolumenfertigung (HVM) bereit sein wird, also erwarten Sie, dass die tatsächlichen Chips, die auf diesem Knoten hergestellt werden, im Jahr 2027 ausgeliefert werden. Vorausgesetzt, Intel hält sein Versprechen und liefert die ersten Chips aus, die mit seinen 20A-Produktionstechnologien (die beide verwenden) hergestellt wurden RibbonFET-GAA-Transistoren und PowerVia-Rückseiten-PDN) im Jahr 2024 wird es TSMC mit rückseitiger Stromschiene zwei oder drei Jahre voraus sein.

N2X: Hochspannung für extreme Leistung

TSMC entwickelt N2X, einen Herstellungsprozess, der auf High-Performance-Computing-Anwendungen (HPC) wie High-End-Rechenzentrums-CPUs zugeschnitten ist. Im Allgemeinen sind diese Chips leistungshungrig und müssen in der Lage sein, ihre Takte bei Spitzenlasten zu erhöhen. Das bedeutet, dass sie hohe Spannungen und Ströme aushalten müssen. Da der Node frühestens 2026 verfügbar sein soll, skizziert TSMC seine Leistungsverbesserungen gegenüber N2, N2P und N3X jetzt nicht. Gleichzeitig können, wie bei allen neueren Produktionstechnologien, maximale Leistung und Effizienz nur durch umfassende Design-Technologie-Co-Optimierung (DTCO) zwischen Foundry und IP-Entwicklern erreicht werden.