Pat Gelsinger, CEO von Intel, zeigte hier auf der Intel Innovation 2023 einen mit Arrow Lake-Testchips gefüllten Wafer, der auf dem 20A-Prozessknoten basiert, und sagte, dass die Chips für die Markteinführung im Jahr 2024 weiterhin auf dem richtigen Weg seien. Wenn Intel mit seinem 20A-Knoten auf dem richtigen Weg bleibe, werde er schlagen TSMC zu zwei entscheidenden neuen Chipherstellungstechnologien. Gelsinger sagte auch, dass Intels Plan, innerhalb von vier Jahren fünf Knoten auszuliefern, auf Kurs bleibe, wobei der Intel 4-Knoten für die Produktion bereit sei und der Intel 3-Knoten für das Jahresende im Zeitplan sei.

Intels Meteor-Lake-Chips der nächsten Generation, die ersten, die den „Intel 4“-Knoten verwenden, sind in Produktion und sollen später in diesem Jahr auf den Markt kommen. Dabei handelt es sich um die ersten Großserien-Consumer-Chips des Unternehmens, die eine Chiplet-basierte Architektur verwenden, die mit der 3D-Foveros-Verbindungstechnologie verbunden ist.

Intels Arrow-Lake-Chips der nächsten Generation basieren auf derselben Designmethodik mit einem neueren Intel 20A-Prozessknoten, der mit zahlreichen neuen Ergänzungen ausgestattet ist, die Intel mit neuer Transistortechnologie an die Spitze von TSMC verhelfen könnten.

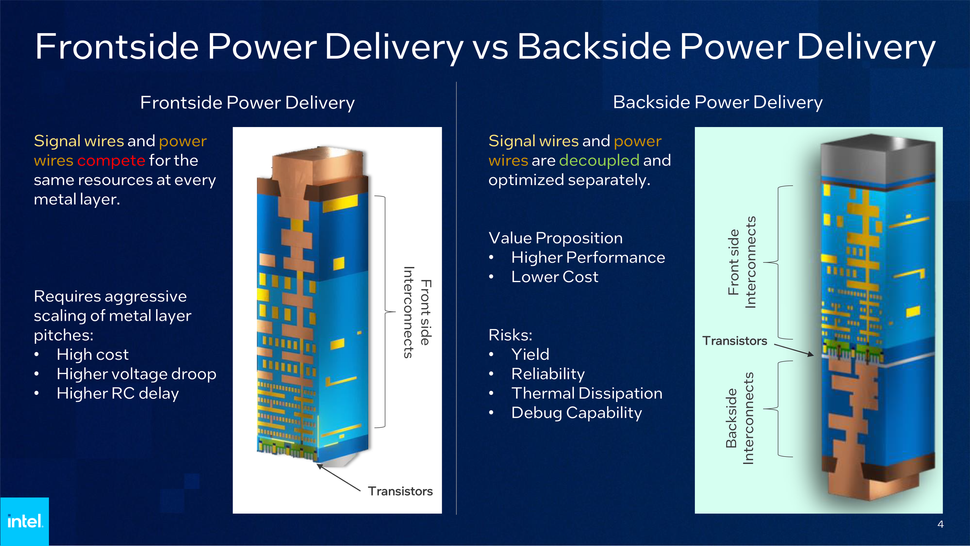

Arrow Lake wird das erste Unternehmen von Intel sein, das den 20A-Knoten (2 nm) von Intel verwendet, der neue Innovationen wie die PowerVia-Stromversorgung auf der Rückseite beinhaltet. Diese Technik leitet den gesamten Strom für die Transistoren direkt durch die Rückseite des Transistors und verteilt die Stromversorgung auf die Rückseite der Transistoren, während die Datenübertragungsverbindungen auf der anderen Seite an ihrem herkömmlichen Standort verbleiben.

Dies bringt eine Reihe von Vorteilen mit sich, darunter die Ermöglichung dichterer Transistoranordnungen, die Verbesserung der Spannungsabfalleigenschaften zur Freigabe höherer Frequenzen und die Ermöglichung eines schnelleren Transistorschaltens bei gleichzeitiger Ermöglichung einer dichteren Signalführung auf der Oberseite des Chips. Auch die Signalübertragung profitiert davon, da die vereinfachte Verlegung schnellere Leitungen mit geringerem Widerstand und geringerer Kapazität ermöglicht.

Intel wird 2024 mit den ersten massenproduzierten Chips mit Backside Power Delivery die Branche anführen. TSMC wird diese Technologie erst 2026 integrieren.

Intels 20A-Prozess beinhaltet auch die RibbonFet Gate-All-Around (GAA)-Technologie, das erste neue Transistordesign von Intel seit der Einführung von FinFET im Jahr 2011. Intels Design besteht aus vier gestapelten Nanoblättern, die jeweils vollständig von einem Gate umgeben sind. Intel behauptet, dass dieses Design ein schnelleres Transistorschalten ermöglicht und dabei den gleichen Antriebsstrom wie mehrere Finnen nutzt, jedoch auf einer kleineren Fläche. Dies erscheint sicherlich plausibel; Wir haben bereits gesehen, dass mehrere Chiphersteller unterschiedliche Varianten dieser Transistortechnologie eingeführt haben.

Intel sagt, dass sein 18A-Knoten weiterhin auf dem richtigen Weg ist, in der zweiten Hälfte des Jahres 2024 produktionsbereit zu sein. TSMC plant, dass sein N2-Knoten mit GAA im Jahr 2025 auf den Markt kommt, sodass er der letzte sein wird, der den neuen Transistortyp einführt. Samsung war das erste Unternehmen, das GAA für den Versand von Produkten herstellte, aber der SF3E-Pfeifenreiniger in geringer Stückzahl wird nicht in Massenproduktion hergestellt. Stattdessen sagt das Unternehmen, dass es noch in diesem Jahr seinen fortschrittlichen Knotenpunkt für die Großserienfertigung vorstellen wird.

Insgesamt ist Intel nach eigenen Angaben auf dem richtigen Weg, sein Ziel zu erreichen, innerhalb von vier Jahren fünf Knoten (technisch gesehen sechs) bereitzustellen. Die feineren Details von Arrow Lake, wie Anzahl und Konfiguration der Kerne, bleiben unbekannt.

Wir sind hier auf der Messe und werden Sie mit weiteren Details zu den neuen Arrow-Lake-Prozessoren informieren, sobald diese auf den Markt kommen.