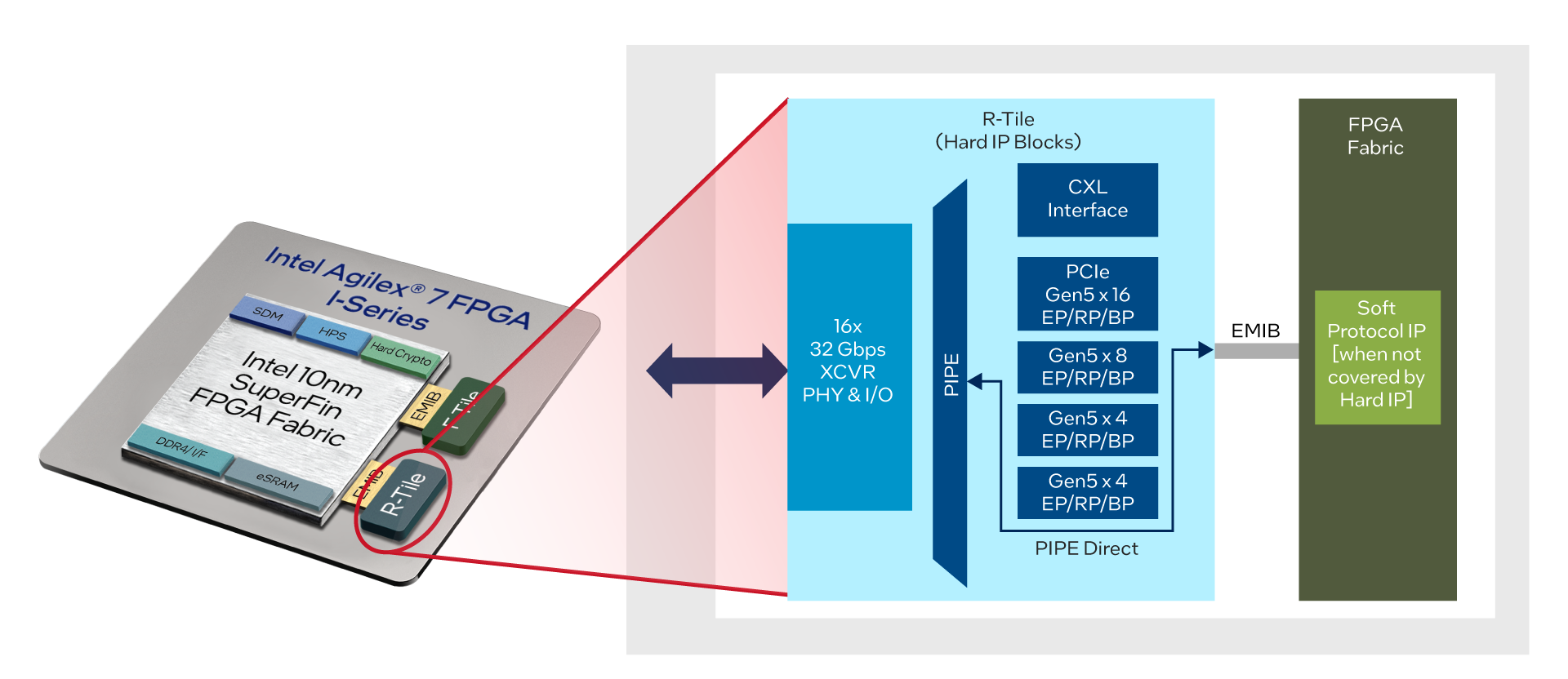

Intel heute bekannt gegeben seine Agilex 7 M-Series-Familie von FPGA-Produkten (Field Programmable Gate Array) und verdoppelt die Kapazität seines revitalisierten 10-nm-SuperFin-Fertigungsknotens. Unter Berufung auf die steigende Marktnachfrage nach FPGA-Lösungen als Co-Prozessoren für Netzwerke, Rechenzentren, High Performance Computing (HPC), Cloud Computing und andere Anwendungen verspricht Intel mehr Flexibilität (hauptsächlich aufgrund der inhärent programmierbaren Natur von FPGAs) und höhere Skalierungsmöglichkeiten als je zuvor. Intels Agilex 7 FPGAs führen einen neuen Chiplet als Teil ihrer heterogenen Multi-Die-Architektur ein. die R-Kacheldas für die Bereitstellung der neuesten Konnektivitätstechnologien – nämlich PCIe 5.0 und CXL-Unterstützung – in hardwarebeschleunigten, hartcodierten IP-Blöcken verantwortlich ist.

Der neue heterogene R-Tile-Chiplet ist für Intel der Star der Show und sichert dem Unternehmen den Titel der einzigen FPGA-Familie, die über eine Zertifizierung für die volle PCI-SIG 5.0 x16-Datenrate verfügt. Xilinx, das jetzt zu AMD gehört, wäre ein Beispiel für einen weiteren führenden FPGA-Entwickler, daher herrscht hier das Gefühl, dass Intel das Rennen gewonnen hat.

Interessanterweise scheint Intel die Trennung zwischen FPGA- und CPU-Produkten zu verstärken. Vielleicht ist das ein Ergebnis seiner früheren Fortschritte in der Integration, von denen nur noch Silikon-Geistergeschichten übrig sind. AMD scheint viel zuversichtlicher zu sein, den Fall gelöst zu haben: Das Unternehmen beabsichtigt offenbar, bereits in diesem Jahr FPGA-Funktionen in seine EPYC-CPUs zu integrieren. Das zementiert jedoch nicht die Abkehr beider Unternehmen – AMD erwägt möglicherweise auch eine Chiplet-ähnliche Integration, sei es vertikal über 3D-Stacking oder durch die Integration getrennter FGPA-spezifischer IP in einen separaten Chip.

Die allgemeine Idee von FPGAs ist ihre inhärente Flexibilität, die es Entwicklern ermöglicht, die Schaltungsanordnung und Verarbeitungsblöcke schnell zu iterieren, um das FPGA an die spezifischen Arbeitslasten anzupassen. Als spezialisiertere Hardware können FPGAs zur Beschleunigung von Arbeitslasten verwendet werden, die nicht von der CPU abhängig sind, wodurch wertvolle CPU-Ressourcen für ihre spezifischen Aufgaben (z. B. das Auslagern von VMs in einer cloudbasierten Installation) frei werden, anstatt deren geringere Leistung zu nutzen Effizienz (die Kosten ihrer allgemeinen Verarbeitungsfähigkeiten).

Intels R-Tile bringt im Wesentlichen die hardwarebeschleunigten IP-Blöcke, die für die Verarbeitung der Protokolle PCIe 5.0 und CXL 1.1/2.0 verantwortlich sind, in seine Agilex 7 FPGA-Familie ein. Dies sollte zu erheblichen Verbesserungen der Energieeffizienz und des Datendurchsatzes führen, die wichtige Elemente zur Senkung der Gesamtbetriebskosten (TCO) von Hochleistungsinstallationen sind. Aber bei diesen Entscheidungen gibt es immer Kompromisse: Intel fügt einem Produkt, dessen Wunsch darin liegt, programmierbar zu sein, einen weiteren Hardwareblock mit fester Funktion hinzu. Programmierbar Die Fläche ist schließlich das Mantra des FPGA-Käufers.

Erwähnenswert ist auch, dass R-Tile als Produkt ausdrücklich sagt: „Ich bin hier, um die Belastung Ihrer CPUs zu reduzieren und gleichzeitig eine höhere Leistung zu liefern.“ Aber eine andere Antwort auf diesen Bedarf besteht nicht darin, CPU-Funktionen in Richtung eines FPGA zu verlagern; Es geht lediglich darum, die Anzahl der verfügbaren CPU-Ressourcen zu erhöhen. Und das könnte mit mehr CPUs (was für einige Installateure sinnvoll sein könnte) oder zusätzlichen CPU-Kernen erreicht werden. Intels Agilex 7 M-Serie ist schließlich speziell für Intels skalierbare Xeon-Prozessoren der 4. Generation vermarktet, und diese sind in keiner Weise die Könige der Kernanzahl.

Intel geht davon aus, dass es auf die oben genannten Fragen eine Antwort gibt und dass das Unternehmen die Antwort kennt: Aus diesem Grund hat es Agilex 7 eingeführt. Die Antwort von Intel lautet, dass Verbraucher den CPU-Overhead reduzieren möchten, indem sie es auf ein FPGA-Gehäuse verlagern. Sie wollen die bestmögliche Leistung/Watt (einer der größten Faktoren für hohe Gesamtbetriebskosten), also bewegen sie die Dinge dorthin, wo sie am schnellsten sind. Glücklicherweise kommt dieser Schritt Intel auch in anderer Hinsicht zugute. Für das Unternehmen ist es eine Frage der eigenen Effizienz – und damit eine Frage der Kosten.

Hier glänzt Intels Embedded Multi-Die Interconnect Bridge (EMIB) wirklich. Als sprichwörtlicher „Klebstoff“, der die unterschiedlichen Verarbeitungsblöcke zusammenhält, ermöglicht EMIB Intel, IP-Blöcke auf der Fertigungsebene weiter zu trennen, wodurch die Chip-Effizienz erhöht und die Gesamtkosten pro Wafer (und die daraus resultierenden Kosten pro Chip) gesenkt werden.

Für den Verbraucher werden dadurch theoretisch auch die Kosten gesenkt: Der Traum von Intel (und der Branche) besteht darin, verschiedene Hardware-IP-Blöcke (vom selben Anbieter oder sogar von mehreren Anbietern und Herstellungsprozessen) kombinieren zu können, sodass Kunden nur bezahlen müssen für das Silizium, das sie tatsächlich verwenden werden, mit den Spezifikationen, die sie tatsächlich verwenden werden. In gewissem Sinne würde dies jeden Chip zu einem FPGA machen.

Vor diesem Hintergrund ist es möglich, dass das heutige Agilex 7 mit R-Tile sowohl ein neues FPGA-Produkt als auch ein neuer Bestandteil im Katalog von Intel Foundry Services (IFS) ist. In jedem Fall bewegt es Intel in die Richtung, in die es gehen will – und muss. Und das ist einfach ein gutes Geschäft.