Indiens Zentrum für die Entwicklung von Advanced Computing (C-DAC) diese Woche angekündigt[PDF] die erste selbst entwickelte High Performance Computing (HPC)-CPU des Landes. Indiens erster Chip mit dem Namen Aum ist ein Chiplet-Design, das auf bis zu 96 Kerne skaliert werden kann und auf Arms v8.4 „Zeus“ Neoverse V1-Designs basiert (die gleichen, die AWS in seinem Graviton3 verwendet) und voraussichtlich als auf den Markt kommen wird bereits 2024 auf dem 5-nm-Prozess von TSMC.

Aum wurde im Rahmen seiner National Supercomputing Mission entwickelt, einem Programm, das darauf abzielt, Indiens Gefährdung durch mögliche Exportbeschränkungen zu verringern. Ziel ist es, eine landesweit entwickelte Prozessorarchitektur einzusetzen. Für Intel und AMD vielleicht alarmierend, besteht das Ziel jedoch darin, dass Aum sowohl in High-Performance-Computing-Szenarien als auch in Personal-Computing-Chips einsetzbar ist. Und wo es Aum gibt, ist der Markt kleiner.

Der Grund dafür ist einfach: Wenn Indien in der Lage ist, Chips zu entwerfen (sei es durch das Mischen und Anpassen von Teilen aus dem offenen Portfolio von Arm oder durch die Führung spezifischer Implementierungen für das endgültige, herstellbare Design), könnten die möglichen technologischen Exportbeschränkungen etwas geringer ausfallen. Gleichzeitig zielt die National Computing Mission auch darauf ab, die Sicherheit vor eventuellen Hintertüren zu verbessern; Ein neutraler Designanbieter wie Arm passt natürlich zu diesen Bedenken. Und auch wenn die Kontrolle des Designprozesses selbst nicht bis zum Ziel reicht (nicht, wenn willige und fähige Gegner Hintertüren in der Fabrikhalle installieren können), ist es ein guter Anfang. Der geplante Einsatz von Open-Source-Software zur Unterstützung eines spezialisierten Software-Ökosystems zeichnet auch eine vielfältigere Software-Zukunft aus, sodass Hardware nicht das einzige Segment ist, das bei genügend Zeit wahrscheinlich fragmentiert wird.

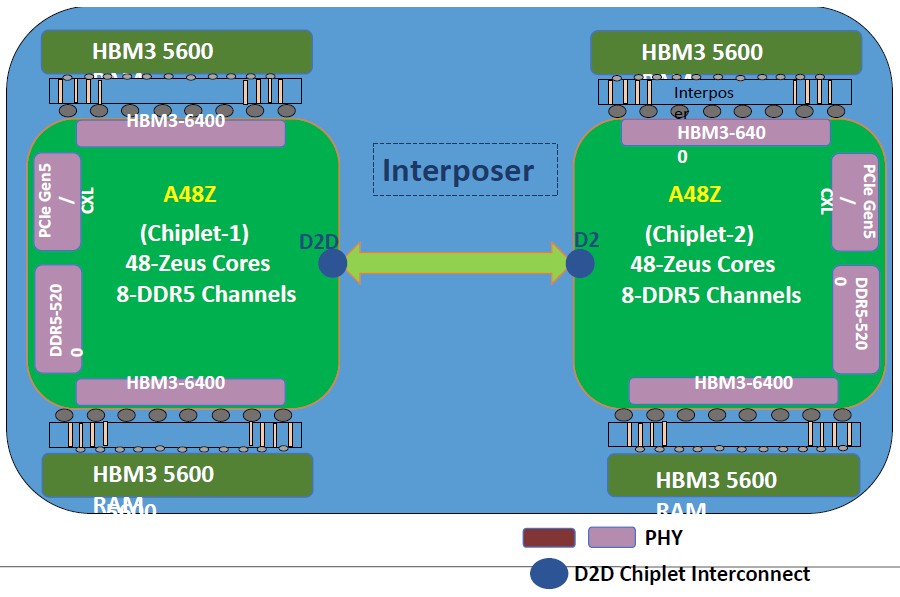

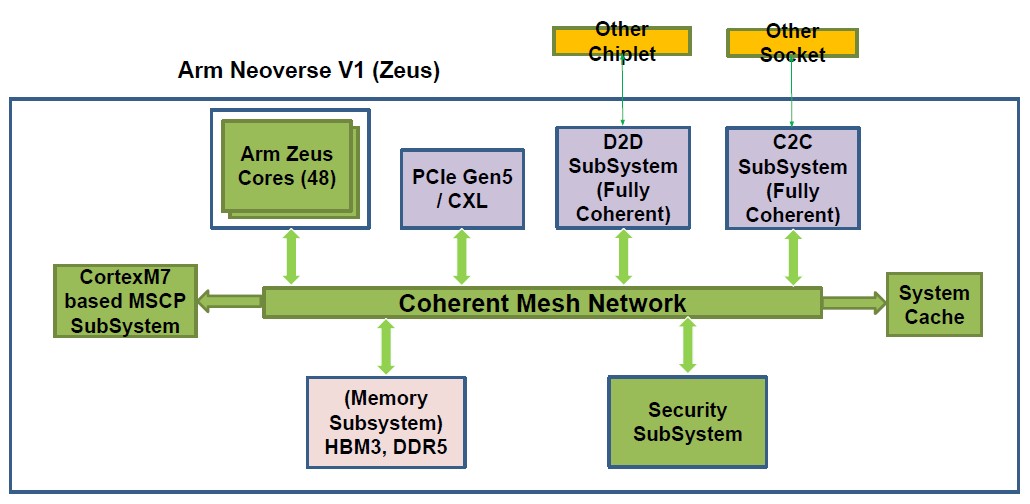

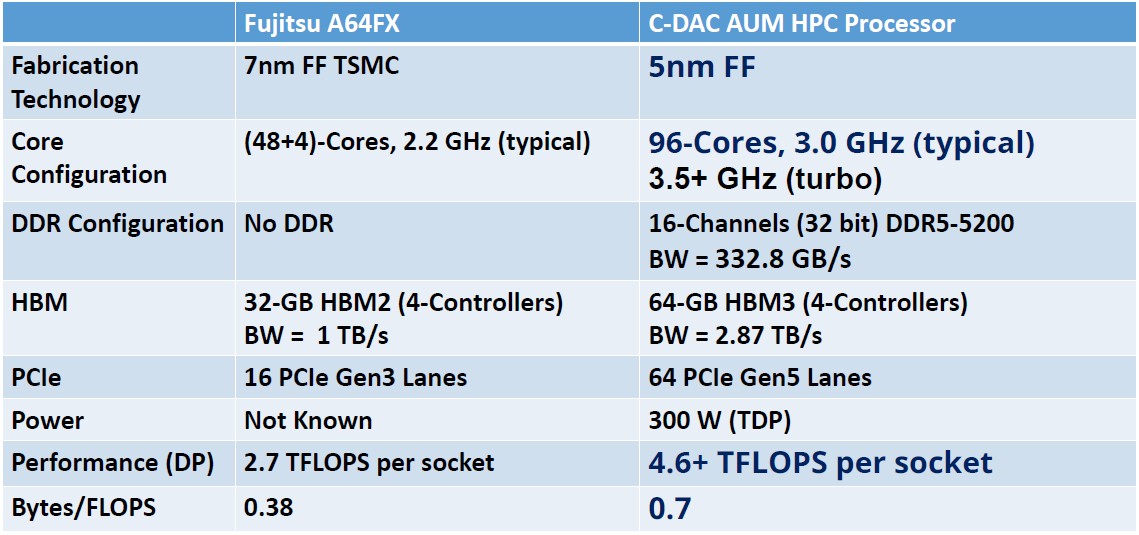

Die A48Z-Chiplets im Herzen des 96-Kern-Aum-Chips verfügen jeweils über 48 Arm-Zeus-Kerne (3-GHz-Basis, 3,5-GHz-Turbo), unterstützt von 96 MB L2-Cache mit sofortigem Zugriff und einer weiteren 96-MB-Cache-Schicht, die die Kerne puffert zusätzlicher Systemspeicher. Alles in allem unterstützt jedes Aum-Paket bis zu 16 DDR5-Speicherkanäle (bei 5200 MHz, liefert 332,8 GB/s Bandbreite) und 64 GB HBM3-Speicher (6,4 GHz Standard, bei der Erstveröffentlichung auf 5,6 GHz reduziert für unglaubliche 2,87). TB/s). Für zusätzlichen Byte-Durchsatz sorgen die 128 PCIe Gen 5-Lanes, von denen 64 zusätzliche Beschleuniger (z. B. GPU- oder FPGA-Beschleuniger) ermöglichen.

Die restlichen 64 werden wahrscheinlich für die interne Kommunikationsstruktur des Chips weitergeleitet, ein kohärentes Mesh-Netzwerk aus NUMA-artigen, vollständig speicherkohärenten Links basierend auf dem CCIX-Protokoll. Diese Verbindung wird von zwei Aum-Sockeln zur Kommunikation genutzt und benötigt ein oder zwei Designseiten von AMDs Infinity Fabric.

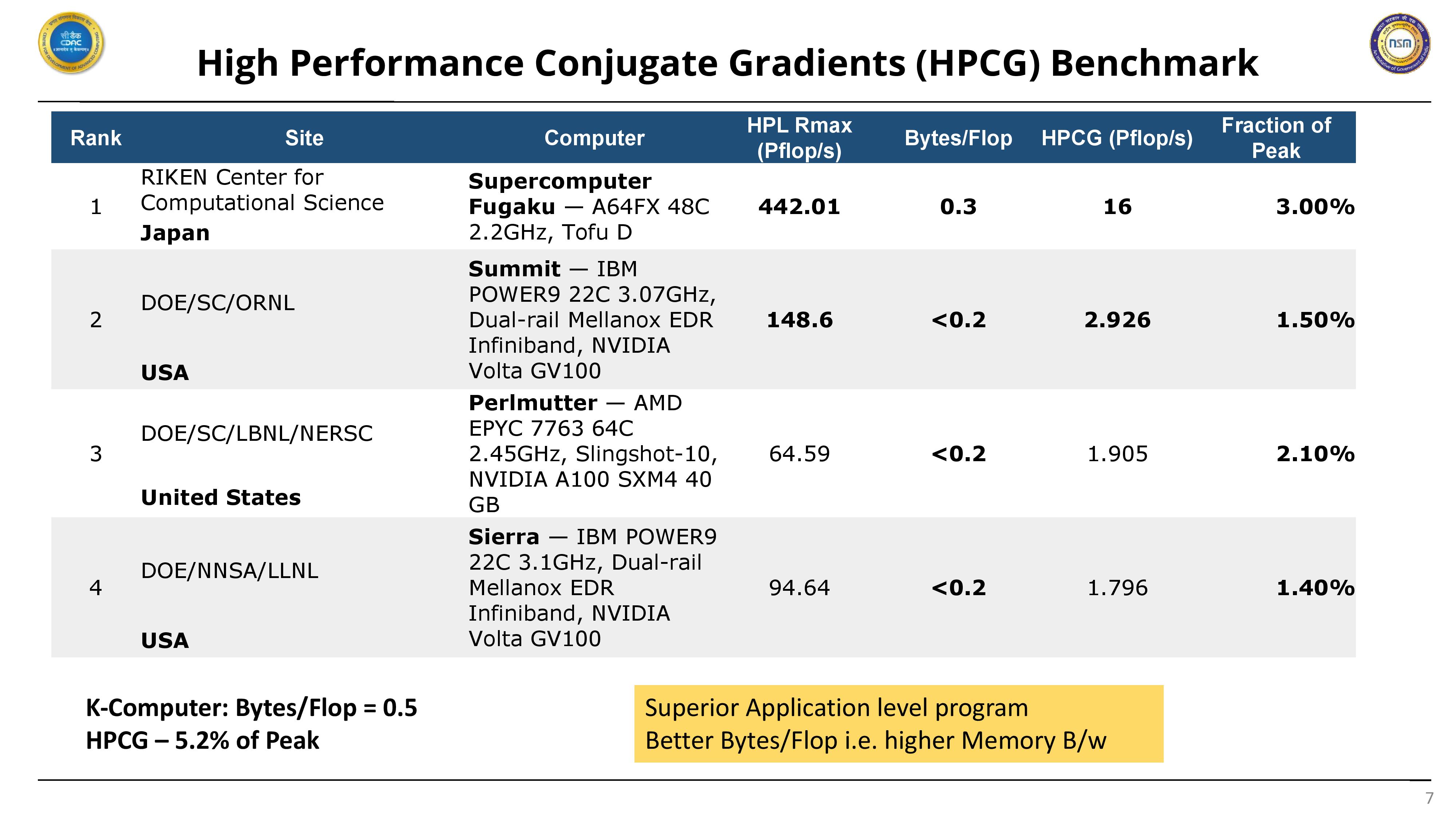

Der Dokumentation zufolge zielt das Design von Aum in erster Linie darauf ab, die pro Flop der Rechenleistung verfügbare Speicherbandbreite (das Byte/Flop-Verhältnis) zu erhöhen, was sich als äußerst limitierender Faktor bei der Leistungsskalierung für HPC-Berechnungen erwiesen hat. Zu viele Autos (schwebende Operationen pro Sekunde) auf zu wenigen Spuren (Speicherdurchsatz) können nur in eine Richtung enden. Das Ergebnis ist, dass Aum und seine Arm-Architektur eine Leistung von 4,6 Teraflops pro Socket und 3 TB/s Gesamtspeicherbandbreite anstreben. Das ergibt ein Byte/Flop-Verhältnis von 0,7, viel höher als die 0,38, die der schnellste Arm-Supercomputer der Welt, Japans Fugaku, erreicht hat, und deutlich besser als der US-amerikanische Summit (<0,2 Bytes/Flop). Bei einer erwarteten TDP von 300 W scheint die Energieeffizienz im Vergleich zu Fugakus A64FX-Arm-Kernen jedoch tatsächlich gesunken zu sein.

Wenn alles nach Plan läuft, wird Indiens Aum Arm-CPU ein starker Einstieg in den Supercomputing-Bereich sein. Entscheidend ist, dass es ein Eigenentwicklungen sein wird – wenn auch nicht dramatisch, zumindest in den ersten Versionen. Offensichtlich wurde viel Arbeit in die Weiterentwicklung des Speichersubsystems als Ganzes gesteckt, und im Allgemeinen ist Speicher einfacher und leichter zu beschaffen als die TSMC-5-nm-Chips, aus denen Aum hergestellt wird. Die Anpassung des CPU-Kerns selbst könnte der nächste Schritt von C-DAC sein, der den Weg für Indien ebnet und dem Prozess der „Chip-Nationalisierung“ in anderen Ländern Schwung verleiht. Übrigens hatte auch China Interesse an Arm; aber das ist eine ganz andere Geschichte.

Dieser umfassendere Drang nach einem vielfältigeren Chip-Ökosystem ist einer der Gründe, warum Intel beschlossen hat, erneut in sein Foundry-Client-Chip-Geschäft zu investieren, ein Schritt, den sein Rivale AMD vor Jahren getan hat (während er sich mitten in einer der schwierigsten Unternehmensumstrukturierungen aller Zeiten befand). . Und es ist ein weiterer Sieg für das Arm-Ökosystem im Vergleich zu seiner manchmal problematischen x86-Alternative, die einige härter als andere bestraft.

Es ist vielleicht auch ein Zeichen für die Zukunft, wenn es um die Liefermengen für Halbleiterhersteller geht: Immer mehr Unternehmen bewerben sich um ihre Entwürfe und erhalten sie aus den Gewässern von TSMC, doch es gibt nur eine begrenzte Anzahl an Wafern für alle Abnehmer – und Krümel von Lautstärkekämpfen liegen bereits auf dem Boden.

Das vollständige Foliendeck folgt.