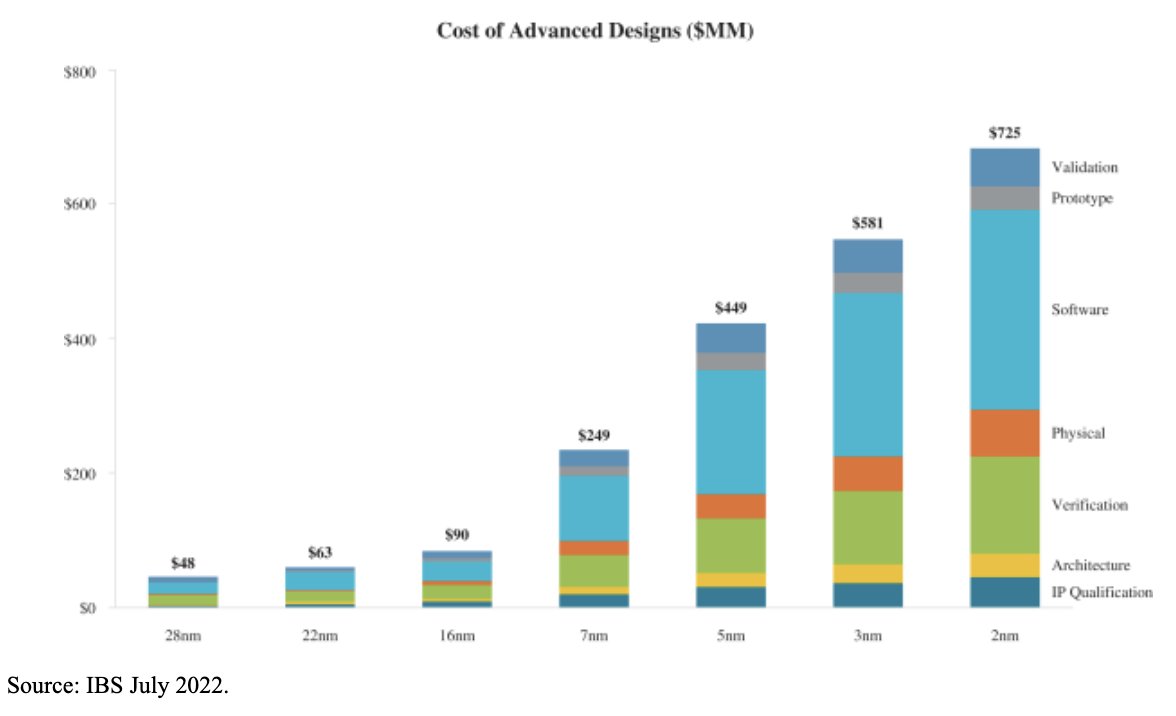

Mit der Einführung von FinFET-Transistoren im Jahr 2014 stiegen die Kosten für das Chipdesign sprunghaft an und stiegen in den letzten Jahren mit Prozesstechnologien der 7-nm- und 5-nm-Klasse besonders stark an. International Business Strategies (IBS) hat kürzlich Schätzungen zu Chipdesigns der 2-nm-Klasse veröffentlicht, und es stellt sich heraus, dass sich die Entwicklung eines ziemlich großen 2-nm-Chips laut einer von veröffentlichten Folie auf insgesamt 725 Millionen US-Dollar belaufen wird Das Transkript.

Die Softwareentwicklung und -verifizierung macht den Löwenanteil der Entwicklungskosten für Chipdesigns aus – etwa 314 Millionen US-Dollar für Software und etwa 154 Millionen US-Dollar für die Verifizierung.

Während die Kosten für das Chipdesign steigen und wir kaum darüber streiten können, gibt es bei den Schätzungen von IBS einen großen Haken. Sie spiegeln die Entwicklungskosten eines ziemlich großen Chips von Grund auf durch ein Unternehmen wider, das über kein geistiges Eigentum verfügt und alles von Grund auf neu entwickeln muss.

Während es Startup-Unternehmen gibt, die es schaffen, riesige Designs zu entwickeln (z. B. Graphcore), entwickeln die meisten von ihnen etwas deutlich Kleineres. Darüber hinaus tendieren Startups dazu, alles zu lizenzieren, was sie können, und müssen daher nur ihr differenzierendes IP entwerfen und verifizieren und dann das gesamte Design validieren. Diese Unternehmen geben nicht 724 Millionen US-Dollar für einen Chip (oder gar eine Plattform) aus, nur weil sie nicht über solche Ressourcen verfügen.

Große Unternehmen, die über Ressourcen für extrem komplexe Chips verfügen, verfügen bereits über jede Menge funktionierendes IP und Codezeilen, sodass sie nicht 724 Millionen US-Dollar für einen einzigen Chip ausgeben müssen. Dennoch neigen sie dazu, Hunderte Millionen oder sogar Milliarden für die Entwicklung von Plattformen auszugeben. Wenn Nvidia beispielsweise seine neuen Produktreihen entwickelt (z. B. Ada Lovelace für Spiele und Hopper für Rechen-GPUs), gibt es enorme Geldbeträge für Mikroarchitekturen und dann für tatsächliche physische Implementierungen von Chips aus.

Ein weiterer Aspekt der Schätzungen besteht darin, dass sie von traditionellen Chip-Design-Methoden ausgehen, ohne KI-gestützte elektronische Design-Automatisierungstools und andere Software zu verwenden, was die Entwicklungszeit und -kosten erheblich senkt. Diese Schätzungen unterstreichen jedoch die Bedeutung KI-fähiger Tools von Ansys, Cadence und Synopsys und deuten darauf hin, dass es in naher Zukunft nahezu unmöglich sein wird, einen Spitzenchip ohne den Einsatz von Software mit künstlicher Intelligenz zu bauen.