Der Occamy-Prozessor, der eine Chiplet-Architektur verwendet, 432 RISC-V- und KI-Beschleuniger enthält und mit 32 GB HBM2E-Speicher ausgestattet ist, wurde abgekündigt. Der Chip wird von der Europäischen Weltraumorganisation unterstützt und von Ingenieuren der ETH Zürich und der Universität Bologna entwickelt, berichtet HPC-Draht.

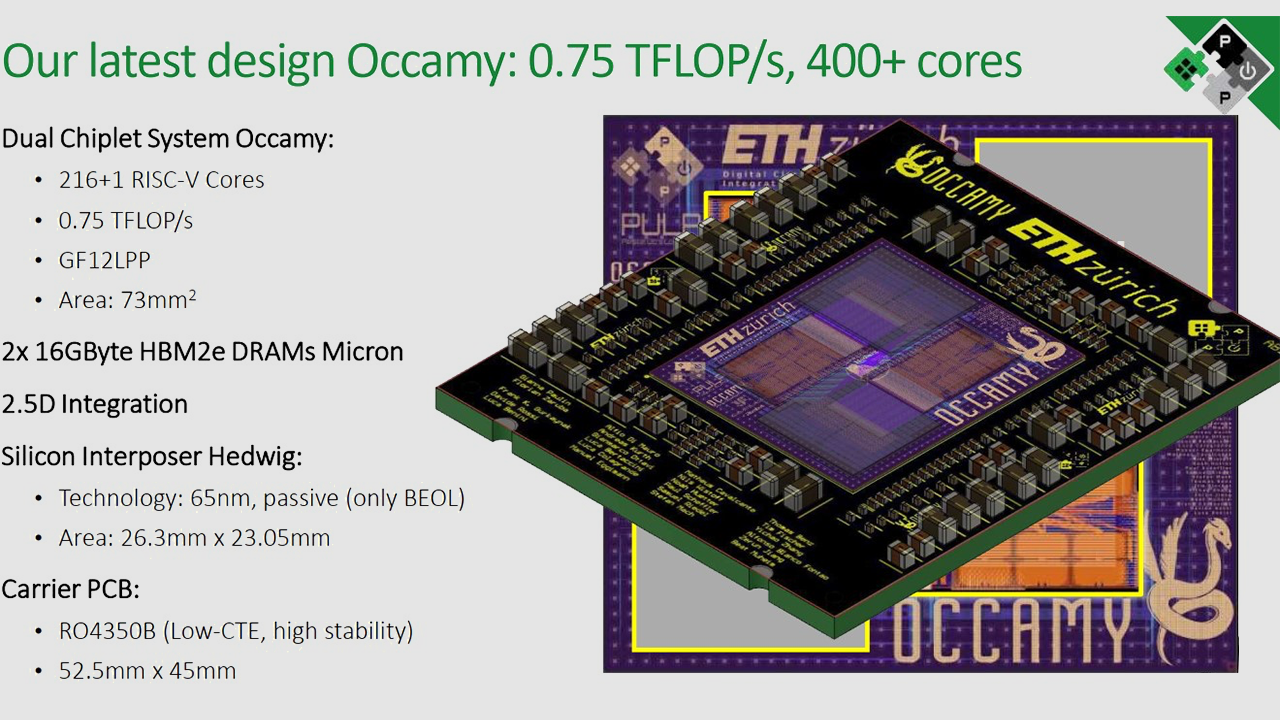

Der von der ESA unterstützte Occamy-Prozessor verwendet zwei Chiplets mit 216 32-Bit-RISC-V-Kernen, eine unbekannte Anzahl von 64-Bit-FPUs für Matrixberechnungen und trägt zwei 16-GB-HBM2E-Speicherpakete von Micron. Die Kerne sind über einen Silizium-Interposer miteinander verbunden, und die Dual-Tile-CPU kann 0,75 FP64 TFLOPS Leistung und 6 FP8 TFLOPS Rechenleistung liefern.

Weder die ESA noch ihre Entwicklungspartner haben den Stromverbrauch der Occamy-CPUs offengelegt, aber es wird gesagt, dass der Chip passiv gekühlt werden kann, was bedeutet, dass es sich um einen Low-Power-Prozessor handeln könnte.

Jedes Occamy-Chiplet verfügt über 216 RISC-V-Kerne und Matrix-FPUs, insgesamt rund eine Milliarde Transistoren, die auf 73 mm² Silizium verteilt sind. Die Fliesen werden von GlobalFoundries im 14LPP-Fertigungsprozess hergestellt.

Das 73 mm^2-Chiplet ist kein besonders großer Chip. Beispielsweise hat Intels Alder Lake (mit sechs Hochleistungskernen) eine Die-Größe von 163 mm^2. In Bezug auf die Leistung liefert Nvidias A30-GPU mit 24 GB HBM2-Speicher 5,2 FP64/10,3 FP64 Tensor TFLOPS sowie 330/660 (mit Sparsity) INT8 TOPS.

Unterdessen besteht einer der Vorteile von Chiplet-Designs darin, dass die ESA und ihre Partner von der ETH Zürich und der Universität Bologna dem Paket weitere Chiplets hinzufügen können, um bei Bedarf bestimmte Arbeitslasten zu beschleunigen.

Die Occamy-CPU wird als Teil des EuPilot-Programms entwickelt und ist einer von vielen Chips, die die ESA für Raumfahrt-Computing in Betracht zieht. Es gibt jedoch keine Garantie dafür, dass das Verfahren tatsächlich an Bord von Raumschiffen verwendet wird.

Das Occamy-Design zielt darauf ab, Hochleistungs- und KI-Workloads durch eine Bare-Metal-Laufzeit zu unterstützen, aber es ist noch nicht klar, ob die Laufzeit auf Containerebene oder auf Bare-Metal-Ebene erfolgen wird. Der Occamy-Prozessor kann auf FPGAs emuliert werden. Die Implementierung wurde auf zwei AMD Xilinx Virtex UltraScale+ HBM FPGAs und dem Virtex UltraScale+ VCU1525 FPGA getestet.