TSMC ist auf dem besten Weg, seine Chip-on-Wafer-on-Substrat-(CoWoS)-Advanced-Packaging-Kapazität bis Ende 2024 um fast das Doppelte zu erweitern, aber selbst dann wird Nvidia die Hälfte der Kapazität verbrauchen, die die Gießerei dann voraussichtlich haben wird DigiTimes.

Berichten zufolge beabsichtigt TSMC, seine CoWoS-Kapazität von heute 8.000 Wafern pro Monat auf 11.000 Wafer pro Monat bis Ende des Jahres und dann auf rund 20.000 bis Ende 2024 zu erweitern. Aber es sieht so aus, als würde Nvidia selbst dann etwa die Hälfte davon nutzen Kapazität, die TSMC haben wird, DigiTimes Behauptungen unter Berufung auf mit der Angelegenheit vertraute Quellen. Unterdessen versucht AMD auch, für nächstes Jahr zusätzliche CoWoS-Kapazität zu buchen.

Megatrends wie 5G, künstliche Intelligenz (KI) und Hochleistungsrechnen (HPC) treiben die Einführung hochkomplexer Multi-Chiplet-Designs wie AMDs Instinct MI300 oder Nvidias H100 voran. Es wird allgemein davon ausgegangen, dass Nvidia der Hauptnutznießer der florierenden Nachfrage nach KI-gebundenen Rechen-GPUs ist und über 90 % der Lieferungen von Rechen-GPUs für neue Bereitstellungen kontrolliert. Infolgedessen hat TSMC Schwierigkeiten, die Nachfrage nach seinen fortschrittlichen CoWoS-Verpackungslösungen zu befriedigen.

TSMC verfügt derzeit über die Kapazität, jeden Monat etwa 8.000 CoWoS-Wafer zu verarbeiten. Nvidia und AMD nutzen zusammen etwa 70 bis 80 % dieser Kapazität und sind damit die dominanten Nutzer dieser Technologie. Danach ist Broadcom der drittgrößte Nutzer und verfügt über etwa 10 % der verfügbaren CoWoS-Waferverarbeitungskapazität. Die verbleibende Kapazität wird auf 20 weitere Fabless-Chip-Designer verteilt.

Verpackungsanlagen für CoWoS und andere fortschrittliche Verpackungstechnologien erfordern spezielle Produktionswerkzeuge und haben Vorlaufzeiten zwischen drei und sechs Monaten. Das bedeutet, dass die Fähigkeit von TSMC, seine CoWoS-Kapazität schnell zu erweitern, begrenzt ist.

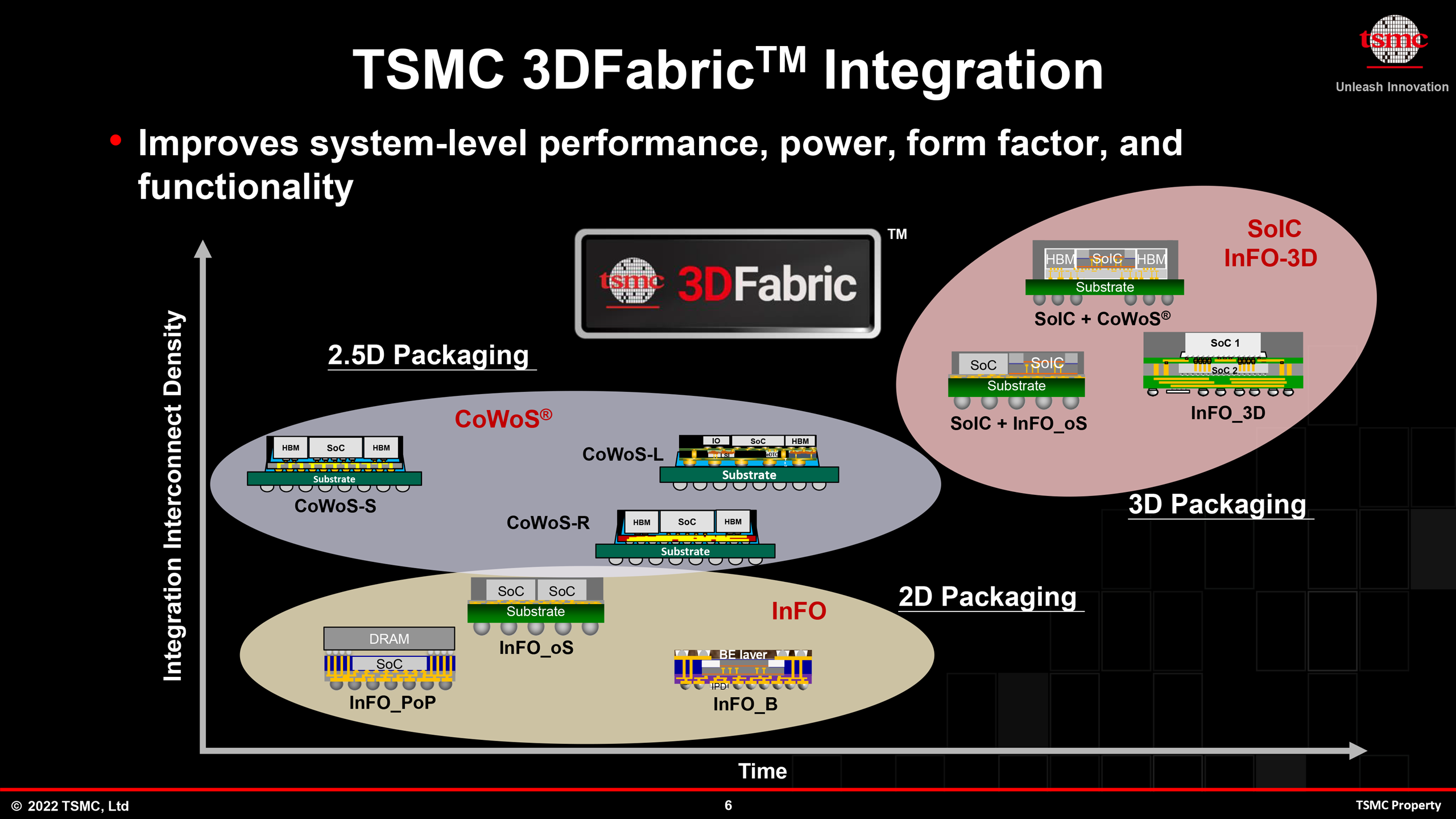

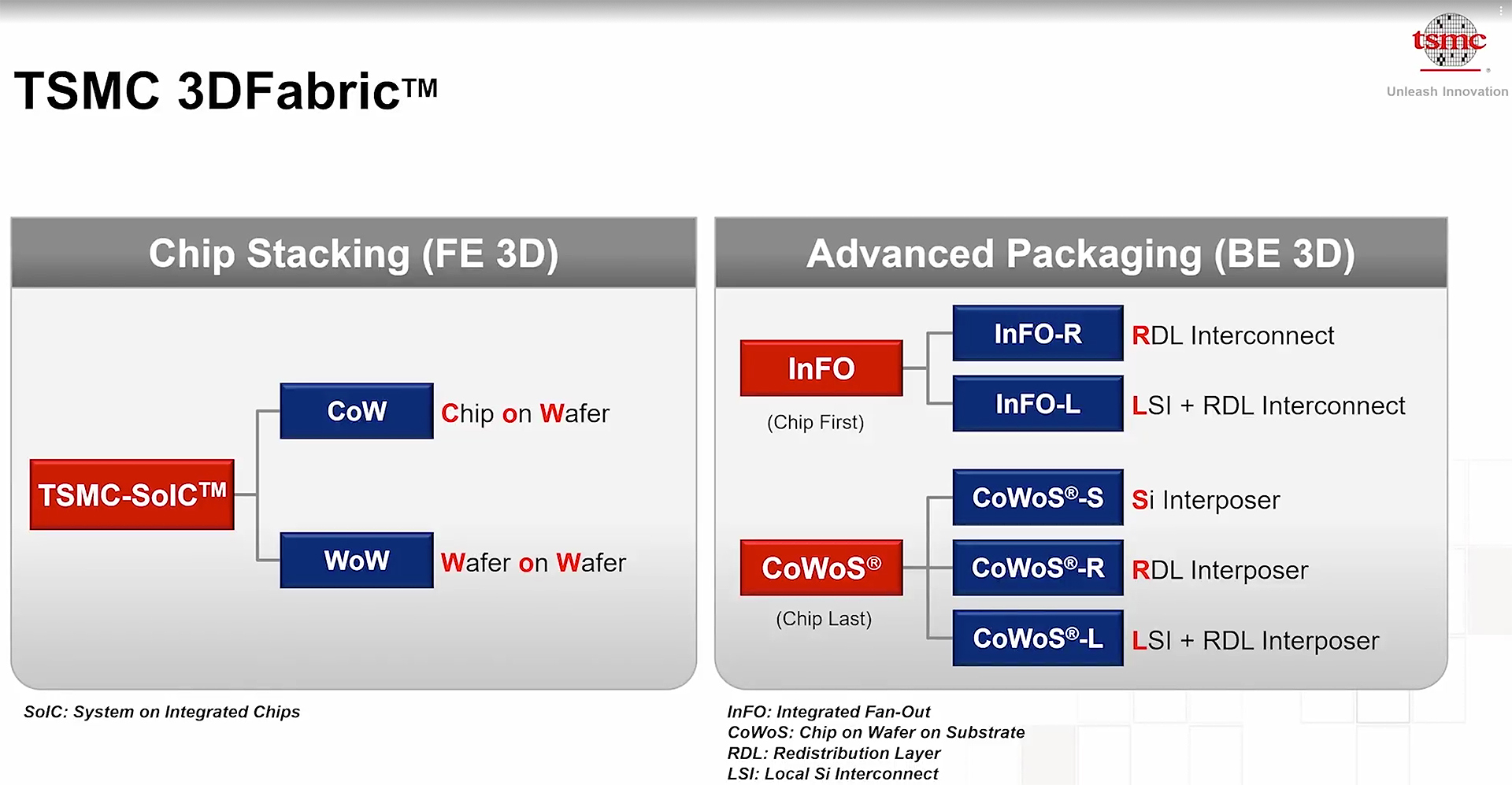

Letzte Woche hat TSMC seine eröffnet Erweiterte Backend-Fab-6-Funktion, das seine fortschrittliche Verpackungskapazität sowohl für seine Frontend-3D-Stacking-SoIC-Technologien (CoW, WoW) als auch für Backend-3D-Verpackungsmethoden (InFO, CoWoS) erweitern wird, aber vorerst ist die Fabrik für SoIC bereit. Das Advanced Backend Fab 6 ist in der Lage, rund eine Million 300-mm-Wafer pro Jahr zu verarbeiten und jährlich über 10 Millionen Teststunden durchzuführen, wobei der Reinraumraum größer ist als der Reinraumraum aller anderen TSMC-Hochleistungsverpackungsanlagen zusammen.

Zu den beeindruckendsten Merkmalen des Advanced Backend Fab 6 gehört das umfassende intelligente automatisierte Fünf-in-Eins-Materialtransportsystem. Das System steuert den Produktionsfluss, erkennt Fehler sofort und erhöht so den Ertrag. Dies ist für komplexe Multi-Chiplet-Baugruppen wie den MI300 von AMD von entscheidender Bedeutung, da Verpackungsfehler alle Chiplets sofort unbrauchbar machen, was zu erheblichen Verlusten führt. Mit Datenverarbeitungsfunktionen, die 500-mal schneller als der Durchschnitt sind, kann die Anlage umfassende Produktionsaufzeichnungen führen und jedes verarbeitete Werkzeug nachverfolgen.

Nvidia nutzt CoWoS für seine äußerst erfolgreichen Rechen-GPUs A100, A30, A800, H100 und H800. AMDs Instinct MI100, Instinct MI200/MI200/MI250X und der kommende Instinct MI300 nutzen ebenfalls CoWoS.