AMD kündigte heute auf seiner Data Center- und AI Technology Premiere-Veranstaltung in San Francisco, Kalifornien, eine Reihe neuer Produkte an. Das Unternehmen teilte schließlich weitere Details zu seinen 5-nm-EPYC-Bergamo-Prozessoren für Cloud-native-Anwendungen mit und die Chips werden jetzt an Kunden ausgeliefert.

AMD kündigte außerdem seine Instinct MI300-Prozessoren an, die über 3D-gestapelte CPU- und GPU-Kerne im selben Paket mit HBM verfügen, sowie ein neues Nur-GPU-MI300X-Modell, das auch dazu dient, acht Beschleuniger auf einer Plattform mit unglaublichen 1,5 TB zu vereinen HBM3-Speicher. AMD kündigte außerdem an, dass seine EPYC Genoa-X-Prozessoren mit bis zu 1,1 GB L3-Cache ausgestattet sind. Alle drei dieser Produkte sind ab sofort erhältlich, aber AMD bringt in der zweiten Hälfte des Jahres 2023 auch seine EPYC-Sienna-Prozessoren für Telekommunikationsunternehmen und Edge auf den Markt.

AMD EPYC Bergamo

Die 128-Kern-EPYC-Bergamo-Prozessoren von AMD sind die branchenweit ersten nativen x86-CPUs, die für die höchste Kerndichte mit einem optimierten Zen 4c-Kern ausgelegt sind, der die für jeden Kern benötigte Fläche halbiert. Diese Chips werden mit Intels 144-Kern-Sierra-Forest-Chips konkurrieren, die das Debüt von Intels Efficiency-Kernen (E-Kernen) in seiner Xeon-Rechenzentrumsreihe markieren, und den 192-Kern-AmpereOne-Prozessoren von Ampre, ganz zu schweigen von dem kundenspezifischen Silizium, das entwickelt wird oder bei Google und Microsoft beschäftigt.

Alle diese Angebote sind darauf ausgelegt, die Energieeffizienz für hochparallele und latenztolerante Arbeitslasten zu maximieren. Beispiele hierfür sind VM-Bereitstellungen mit hoher Dichte, Datenanalysen und Front-End-Webdienste. Die Chips bieten eine höhere Kernzahl als Standard-Rechenzentrumslösungen bei geringerer Frequenz und geringerem Leistungsumfang.

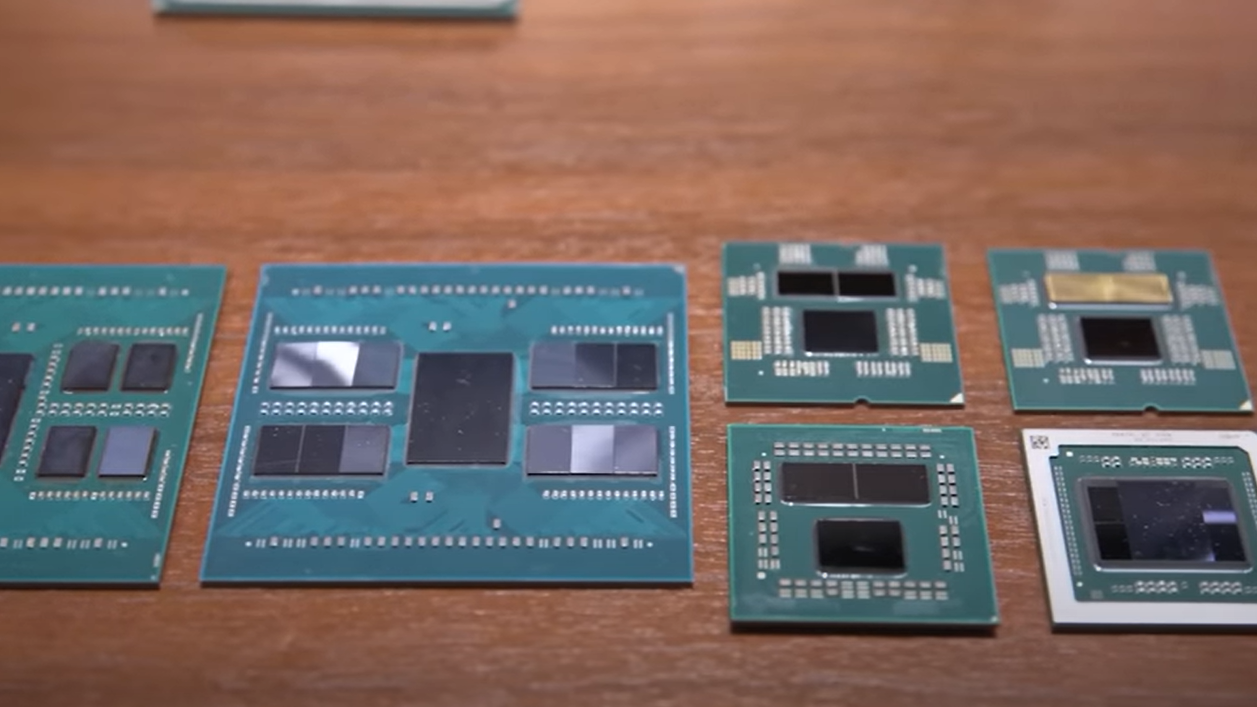

AMDs Bergamo verfügt über 128 Kerne und lässt sich in Serverplattformen integrieren, die denselben Sockel SP5 wie die standardmäßigen 96-Kern-EPYC-Genoa-Prozessoren verwenden. Wie ihre regulären Pendants unterstützt Bergamo 12-Kanal-Speicher mit DDR5-4800. AMD schmiedet die Chips, indem es Chiplets mit Zen 4c-Kernen mit dem vorhandenen zentralen I/O-Chip „Floyd“ des Unternehmens kombiniert und so die Rechenchiplets an einen Speicher- und I/O-Chiplet bindet, der auf einem älteren Prozessknoten basiert.

| Zeile 0 – Zelle 0 | Kerne / Max. Threads | Basis/Boost (GHz) | Standard-TDP | L3-Cache |

| 9754 | 128 / 256 | 2,25 / 3,1 | 360W | 256 MB |

| 9754S | 128 / 128 | 2,25 / 3,1 | 360W | 256 MB |

| 9734 | 112 / 224 | 2,2 / 3,0 | 320W | 256 MB |

AMD hat vorerst die beiden oben genannten Bergamo-Prozessoren angekündigt, den EPYC 9754 mit 128 Kernen/256 Threads und den EPYC 9734 mit 112 Kernen/224 Threads. Letzterer hat zwei Kerne pro deaktiviertem CCD. Die meisten verbleibenden Spezifikationen außer der Kernanzahl sind gleich, sodass der 9734 immer noch über die vollen 16 MB L3-Cache pro CCX und insgesamt 256 MB L3-Cache verfügt. AMD behauptet mit den Bergamo-Chips eine 2,7-fache Steigerung der Energieeffizienz.

AMD teilte ein paar grobe Bemerkungen zur Bergamo-Architektur mit, unter anderem, dass sie über eine Kern- und L3-Cache-Fläche von 2,48 mm^2 verfügt, was 35 % kleiner ist als die 3,84 mm^2, die sie auf demselben Prozessknoten mit dem Standard-Zen erreichte 4 Kerne. AMD verwendet acht 16-Kern-CCDs, um die maximale Kernzahl von 128 Kernen zu erreichen.

Interessant ist auch, dass AMD derzeit nur acht Zen 4C-Chiplets mit dem zentralen IO-Chiplet verwendet, während die Standard-EPYC-Chips bis zu zwölf Zen 4-Chiplets verwenden. Könnten wir eine zukünftige Zen 4C-Lösung mit zwölf Chiplets und 192 Kernen sehen? Vielleicht, aber AMD hat ein solches Design noch nicht angekündigt, also müssen wir abwarten und sehen.

Wir lernen heute tiefergehende Architekturdetails der Chips kennen, bleiben Sie dran für weitere Berichterstattung.