Um die Nachfrage nach Rechen-GPUs und anderen Prozessoren für KI und HPC zu decken, hat TSMC kürzlich zusätzliche Tools für die Chip-on-Wafer-on-Substrat-Verpackung (CoWoS) bestellt, wie in der jüngsten Gewinnmitteilung angegeben . Besonders optimistisch scheint das Unternehmen hinsichtlich der Nachfrage nach den kommenden Rechenzentrums-APUs und GPUs der Instinct MI300-Serie von AMD zu sein. DigiTimes Berichten zufolge wird es die Hälfte von Nvidias Gesamtproduktion an CoWoS-verpackten Chips ausmachen.

Diese anhaltende Expansion wurde durch die bevorstehende Massenproduktion der MI300-Serie von AMD und den anhaltenden Mangel an Chip-on-Wafer-on-Substrat (CoWoS)-Verpackungskapazitäten ausgelöst, der durch die Anforderungen von Nvidia noch verschärft wurde. DigiTimes geht unter Berufung auf Quellen aus der Branche sogar so weit, zu sagen, dass, wenn AMDs MI300-Serie in die Massenproduktion geht, das Volumen der TSMC-Lieferungen für dieses CoWoS-basierte Produkt der Hälfte der gesamten mit CoWoS ausgestatteten GPU von Nvidia in einem einzigen Stück entsprechen wird Quartal.

Dies deutet im Wesentlichen darauf hin, dass die Nachfrage nach AMDs Rechen-GPU der nächsten Generation die Hälfte der von Nvidia gelieferten CoWoS-GPUs ausmachen wird, was eine sehr optimistische Erwartung ist, da Nvidia heute aufgrund der Dominanz seiner CUDA-Software über 90 % des Rechen-GPU-Marktes beherrscht Top-Stapel unter den KI- und HPC-Entwicklern.

Um seine CoWoS-Kapazität zu erweitern, hat TSMC laut DigiTimes kürzlich neue Aufträge bei Lieferanten fortschrittlicher Verpackungsausrüstung aufgegeben, darunter Apic Yamada, Disco, Gudeng Precision Industrial und Scientech. Die Vorlaufzeit für solche Werkzeuge beträgt derzeit weniger als sechs Monate China Renaissance Securities. Neben AMD und Nvidia nutzen auch Amazon, Broadcom und Xilinx CoWoS-Pakete für ihre Rechenzentrumsangebote.

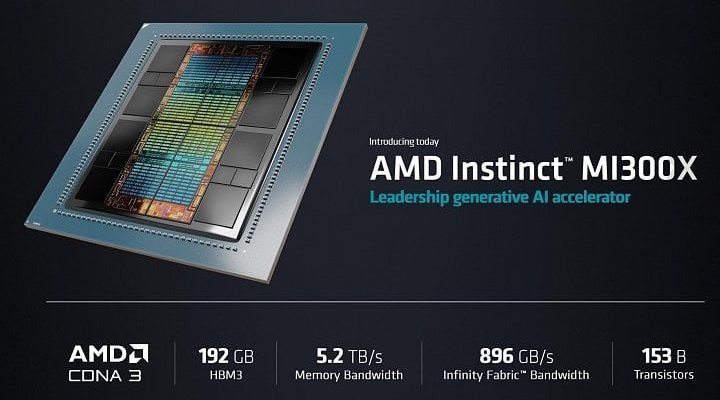

Die CoWoS-Verpackungstechnologie von TSMC wird verwendet, um Instinct MI250/MI300-Chiplets zusammenzufügen und HBM-Speicher mit Rechenkacheln der Lösung zu verbinden. Ohne CoWoS-Paketierung ist es unmöglich, die Produkte der Serien MI200 und MI300 von AMD sowie die Rechen-GPUs von Nvidia zu bauen, die auf HBM-Speicher basieren.

Basierend auf inoffiziellen Informationen beabsichtigt TSMC, seine bestehende CoWoS-Kapazität bis Ende 2023 von 8.000 Wafern pro Monat auf 11.000 Wafer pro Monat zu erhöhen. Anschließend ist geplant, diese Zahl bis Ende 2024 weiter auf 14.500 bis 16.600 Wafer zu erhöhen, so ein anderes Gerücht . Zuvor gab es Gerüchte, dass Nvidia seine CoWoS-Kapazität bis Ende 2024 auf 20.000 Wafer pro Monat erweitern wollte. TSMC gibt unterdessen lediglich an, dass es plant, die CoWoS-Kapazität bis Ende 2024 zu verdoppeln.

Die Aktien von AMD verzeichneten am Dienstag im nachbörslichen Handel einen Anstieg von 4 %, nachdem das Unternehmen ein „sehr großes“ Kundeninteresse an seiner bald auf den Markt kommenden APU und GPU der Instinct MI300-Serie bekannt gegeben hatte, die voraussichtlich in Produktion gehen wird das vierte Viertel. Allerdings gab die Aktie am Mittwoch um etwa 6 % nach, da Analysten Zweifel an den KI-Eskalationszielen des Chip-Designers äußerten und sie für möglicherweise zu optimistisch hielten. Reuters Berichte.

„Wir befürchten, dass die Schätzungen zu hoch bleiben und die AMD-Aktie für uns etwas überzogen erscheint, es sei denn, die Zahlen werden bald wirklich aussagekräftig“, schrieben die Analysten von Bernstein in einer Notiz Reuters.