Der erste und angebliche Leistungsbenchmark eines AMD Zen 5-Systems mit zwei EPYC Turin-CPUs der nächsten Generation ist durchgesickert Moores Gesetz ist tot.

AMDs duale EPYC Turin ES-CPUs mit Zen 5-Core-Architektur, angeblich Benchmarking, schneller als 96-Core-Genoa-Chips

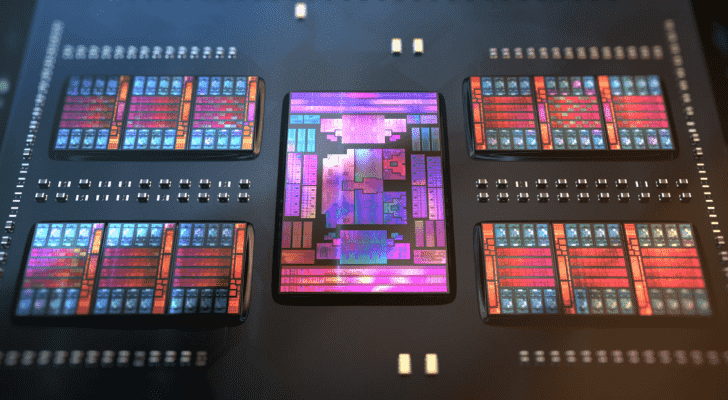

Laut Moore’s Law is Dead hat die Gerüchteküche scheinbar die ersten AMD Zen 5-CPU-Benchmarks erhalten. Die Benchmarks stammen nicht von einem Ryzen-Chip auf Verbraucherebene, sondern von einer EPYC-Dual-System-Konfiguration. Der gemunkelte Chip könnte Teil der AMD EPYC Turin-Familie sein, die voraussichtlich nächstes Jahr auf den Markt kommt.

Bevor wir also über Benchmarks sprechen, müssen wir über die Spezifikationen sprechen, die dieser angebliche Chip bietet. Zunächst einmal handelt es sich bei der CPU um ein sehr frühes Engineering-Sample, sodass sich zwischen jetzt und während der Markteinführung viel ändern kann. Die AMD EPYC Turin ES-CPU mit Zen 5-Kernarchitektur verfügt über 64 Kerne und 128 Threads, und da es sich um eine Dual-Socket-Konfiguration handelt, wird sie mit 128 Kernen und 256 Threads angezeigt. Jeder Chip trägt die gleiche Menge an L2- und L3-Cache wie die Zen-4-Kerne, aber der L1-Cache sieht ein kleines Upgrade vor.

Der L1-Cache steigt von 64 KB auf Zen 4 auf 80 KB auf Zen 4, was eine Steigerung von 25 % bedeutet. Der L2-Cache beträgt 64 MB pro Chip (1 MB pro Kern) und der L3-Cache 256 MB (4 MB pro Kern). Die CPU-Takte scheinen mit 2,3 GHz Basis und 3,85 GHz Boost bewertet zu sein, was für ein technisches Muster einer CPU, die in mehr als einem Jahr veröffentlicht wird, sehr hoch erscheinen mag. Das ist bereits 4 % höher als die Boost-Takte des AMD EPYC 9654 Genoa-Chips, aber während einer kürzlichen Projektionsfolie wies Ex-AMD-Architekt Jim Keller darauf hin, dass Zen 5 die 4-GHz-Taktgrenze auf Servern entweder erreichen oder überschreiten könnte.

Kommen wir nun zur Hauptaktion, dem Leistungsbenchmark, das duale AMD EPYC Turin-System mit Zen 5-CPUs wurde in Cinebench R23 getestet und erzielte etwa 123.000 (~ 123.000) Punkte. Im Vergleich zu den dualen 96-Core-EPYC-Genoa-Chips sind die EPYC-Turin-64-Core-Chips bereits in ihrem ES-Zustand schneller als ihre Vorgänger.

0

20500

41000

61500

82000

102500

123000

Dies ist in der Tat ein beeindruckendes Schaufenster von AMDs Zen 5-CPUs, aber wir müssen bedenken, dass dies vorerst nur ein Gerücht ist. Wenn sich herausstellt, dass dies tatsächlich der Fall ist, wird Zen 5 ein komplettes Biest sein, und das sollte es auch sein, da es eine von Grund auf neu aufgebaute Architektur unter einer Liste von Dingen aufweist. Die Verkaufsstelle gibt auch an, dass Zen 5 Turin 8-Kern-CCDs verwenden wird, Zen 5C Turin-Dense voraussichtlich 16-Kern-CCXs verwenden wird und dass das Unternehmen einen 3-nm-16-Kern-CCX in Arbeit hat, obwohl daran erinnert werden sollte, dass AMD dies tun wird haben Zen 5 sowohl auf 4-nm- als auch auf 3-nm-Knoten.

AMD Zen 5 im Jahr 2024 mit V-Cache- und Compute-Varianten mit brandneuer Mikroarchitektur

AMD hat bisher bestätigt, dass die neue Zen 5-Architektur im Jahr 2024 auf den Markt kommen wird. Die Zen 5-CPUs werden in drei Geschmacksrichtungen (Zen 5 / Zen 5 V-Cache / Zen 5C) erhältlich sein, und der Chip selbst ist von Grund auf neu konzipiert Eine völlig brandneue Mikroarchitektur, die sich auf die Bereitstellung verbesserter Leistung und Effizienz, eines neu geordneten Front-Ends und eines breiten Problems zusammen mit integrierter KI und maschineller Lernoptimierung konzentriert. Einige der Hauptmerkmale von Zen 5-CPUs sind:

- Verbesserte Leistung und Effizienz

- Re-pipelined Frontend und Wide Issue

- Integrierte Optimierungen für KI und maschinelles Lernen

AMD EPYC CPU-Familien:

| Familienname | AMD EPYC Venedig | AMD EPYC Turin | AMD EPYC Siena | AMD EPYC Bergamo | AMD EPYC Genua-X | AMD EPYC Genua | AMD EPYC Milan-X | AMD EPYC Mailand | AMD EPYC Rom | AMD EPYC Neapel |

|---|---|---|---|---|---|---|---|---|---|---|

| Familienmarke | EPYC 11K? | EPYC 10K? | EPYC 9000? | EPYC 9000? | EPYK 9004 | EPYK 9004 | EPYK 7004 | EPYK 7003 | EPYK 7002 | EPYK 7001 |

| Familienstart | 2025+ | 2024 | 2023 | 2023 | 2023 | 2022 | 2022 | 2021 | 2019 | 2017 |

| CPU-Architektur | Zen6? | Zen 5 | Zen 4 | Zen 4C | Zen 4 V-Cache | Zen 4 | Zen 3 | Zen 3 | Zen 2 | Zen 1 |

| Prozessknoten | offen | 3-nm-TSMC? | 5-nm-TSMC | 4-nm-TSMC | 5-nm-TSMC | 5-nm-TSMC | 7-nm-TSMC | 7-nm-TSMC | 7-nm-TSMC | 14 nm GloFo |

| Plattformname | offen | SP5 / SP6 | SP6 | SP5 | SP5 | SP5 | SP3 | SP3 | SP3 | SP3 |

| Steckdose | offen | LGA 6096 (SP5) LGA XXXX (SP6) |

LGA4844 | LGA6096 | LGA6096 | LGA6096 | LGA 4094 | LGA 4094 | LGA 4094 | LGA 4094 |

| Max. Kernzahl | 384? | 128? | 64 | 128 | 96 | 96 | 64 | 64 | 64 | 32 |

| Maximale Fadenzahl | 768? | 256? | 128 | 256 | 192 | 192 | 128 | 128 | 128 | 64 |

| Maximaler L3-Cache | offen | offen | 256MB? | offen | 1152MB | 384MB | 768MB | 256MB | 256MB | 64MB |

| Chiplet-Design | offen | offen | 8 CCDs (1CCX pro CCD) + 1 IOD | 12 CCDs (1 CCX pro CCD) + 1 IOD | 12 CCDs (1 CCX pro CCD) + 1 IOD | 12 CCDs (1 CCX pro CCD) + 1 IOD | 8 CCDs mit 3D V-Cache (1 CCX pro CCD) + 1 IOD | 8 CCDs (1 CCX pro CCD) + 1 IOD | 8 CCDs (2 CCXs pro CCD) + 1 IOD | 4 CCDs (2 CCXs pro CCD) |

| Speicherunterstützung | offen | DDR5-6000? | DDR5-5200 | DDR5-5600? | DDR5-4800 | DDR5-4800 | DDR4-3200 | DDR4-3200 | DDR4-3200 | DDR4-2666 |

| Speicherkanäle | offen | 12 Kanäle (SP5) 6-Kanal (SP6) |

6-Kanal | 12 Kanäle | 12 Kanäle | 12 Kanäle | 8 Kanäle | 8 Kanäle | 8 Kanäle | 8 Kanäle |

| PCIe-Gen-Unterstützung | offen | offen | 96 Gen 5 | 160 Gen 5 | 128 Gen 5 | 128 Gen 5 | 128 Gen 4 | 128 Gen 4 | 128 Gen 4 | 64 Gen 3 |

| TDP (max.) | offen | 480 W (cTDP 600 W) | 70-225 W | 320 W (cTDP 400 W) | 400W | 400W | 280W | 280W | 280W | 200W |