TSMC offengelegt wichtige Roadmap-Updates für seine N3-Familie (3-Nanometer-Klasse) von Prozesstechnologien auf seinem North American Technology Symposium 2023 in dieser Woche. Als letzter Hochleistungsknoten von TSMC auf Basis von FinFET-Transistoren wird N3 viele Jahre halten und mehrere Versionen umfassen, darunter N3P, eine leistungssteigernde optische Verkleinerung von N3E, und leistungsorientiertes N3X für HPC-Anwendungen, die hohe Leckage und Leistung tolerieren .

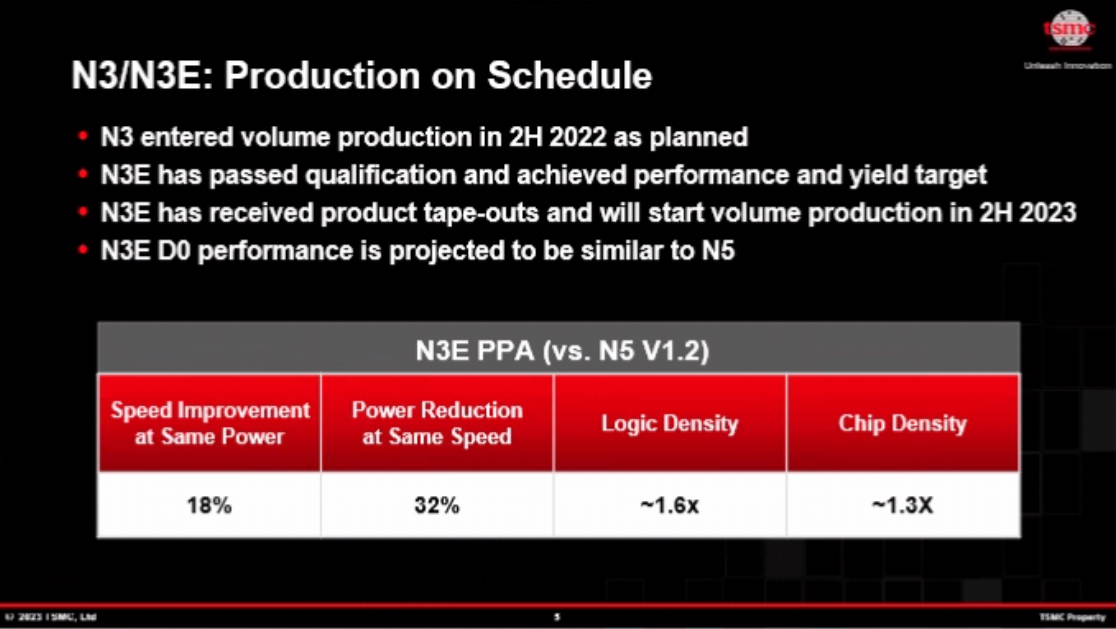

Die Massenproduktion von TSMC mit seiner N3-Prozesstechnologie (auch bekannt als N3B) ist bereits im Gange, aber dieser Knoten verwendet extreme Ultraviolett-Lithographie auf bis zu 25 Schichten und kann sogar EUV-Doppelmuster verwenden, was ihn zu einem besonders teuren Knoten macht. Infolgedessen erwartet TSMC, dass die Mehrheit seiner Kunden N3E verwenden wird, das EUV auf bis zu 19 Schichten verwenden kann, kein EUV mit doppelter Musterung verwendet, ein breiteres Prozessfenster und bessere Erträge hat. N3E, das im zweiten Halbjahr 2023 für die Massenfertigung verwendet wird, wird auch die Basis für die weitere 3-nm-Entwicklung von TSMC sein.

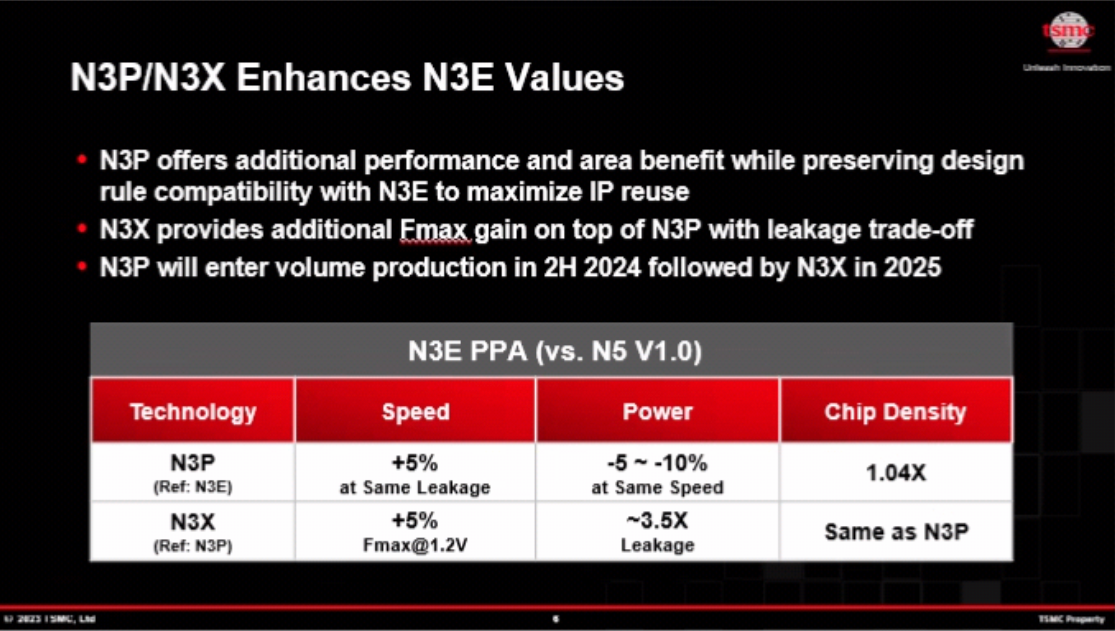

Der erste Schritt in dieser Entwicklung wird N3P sein. Diese Technologie wird größtenteils eine optische Verkleinerung von N3E sein, die einige andere Verfeinerungen aufweisen wird, die eine Leistungssteigerung von 5 % bei gleicher Leckage, eine Leistungsreduzierung von 5 % bis 10 % bei gleichen Takten und eine 4 % höhere Transistordichte für eine ‘ gemischter Chip bestehend aus 50 % Logik, 30 % SRAM und 20 % analogen Schaltungen.

Als optische Verkleinerung von N3E behält N3P seine Designregeln bei, sodass Chipdesigner N3E-IP auf dem neuen Knoten wiederverwenden können. Dies ist ziemlich wichtig, da IP-Designunternehmen wie Ansys, Cadence und Synopsys bereits viele IPs für N3E-Chips haben. In der Zwischenzeit impliziert optisches Schrumpfen eine Verbesserung der Dichte für alle Arten von Transistoren und Schaltungen, einschließlich SRAM, einer Art von Schaltungen, die in den letzten Jahren mit dem Schrumpfen zu kämpfen hatte (was für moderne SRAM-intensive Designs besonders schlimm ist). N3P wird 2024 serienreif sein.

Nach N3P plant TSMC, seine N3-Familie weiter auszubauen und sie mit N3X in Hochleistungs-Computing-Anwendungen wie CPUs und GPUs zu verzweigen. Dieser Herstellungsprozess soll im Vergleich zu N3P mindestens 5 % höhere Frequenzen liefern und auch erheblich höhere Spannungen ermöglichen, was die Taktraten auf Kosten höherer Gesamtverluste weiter erhöhen wird.

| Zeile 0 – Zelle 0 | N3X gegen N3P | N3P gegen N3E | N3E gegen N5 | N3 gegen N5 |

| Geschwindigkeitsverbesserung bei gleicher Leistung | +5 % Fmax bei 1,2 V | +5 % | +18% | +10 % ~ 15 % |

| Leistungsreduzierung bei gleicher Geschwindigkeit | ? | -5 % ~ -10 % | -32% | -25 % ~ -30 % |

| Logikdichte | Dasselbe | 1,04x | 1,7x | 1,6x |

| HVM starten | 2025 | H2 2024 | Q2/Q3 2023 | H2 2022 |

TSMC behauptet, dass sein N3X-Knoten mindestens 1,2 V verarbeiten kann, eine bemerkenswert hohe Spannung für eine Fertigungstechnologie der 3-nm-Klasse. Dies ist mit einem erheblichen Kompromiss verbunden, da TSMC im Vergleich zu N3P einen umwerfenden Anstieg der Verlustleistung um 250 % erwartet. Dies unterstreicht, dass N3X in erster Linie für HPC-CPUs geeignet ist und Chipdesigner bei der Entwicklung ihrer leistungshungrigsten Chips, wie Rechenzentrums-CPUs und Rechen-GPUs, Vorsicht walten lassen müssen.

In Bezug auf die Transistordichte wird N3X den Fähigkeiten von N3P entsprechen. TSMC hat nicht angegeben, ob sein N3P und N3E kompatible Designregeln haben werden, was Raum für Intrigen darüber lässt, ob Designs zwischen den beiden Knoten portiert werden können.